## A SYSTEMATIC APPROACH TO THE MANAGEMENT OF DATA ON DISTRIBUTED DATA BASES

#### Benjamin Wan-Sang Wah

Electrical Engineering and Computer Science

Sponsors: Ballistic Missile Defense Army Research Office National Science Foundation

> C. V. Ramamoorthy Chairman of Committee

## ABSTRACT

Recent studies have revealed that the design of a distributed data base management system is a major source of difficulty in designing a distributed computer systems. Research has involved an investigation of the data management issues, examining in particular the *query decomposition*, the *file placement*, the *task scheduling*, and the *hardware support* issues. The inherent relationships among these issues are analyzed and a unified approach is provided to design data management strategies on distributed data bases.

One of the major problems in distributed computer systems is the minimization of communication overheads among nodes. This is the objective of the study in query decomposition and file placement and migration. Two complementary techniques are developed in query decomposition so that nondecomposable queries which require the use of multiple files can be decomposed into multiple sub-queries which require the use of single file. The communication overheads are reduced because the queries do not have to be processed at a common location and can be distributed to the different nodes on the distributed system. The study of query decomposition has also shown that the placements of multiple files can be decomposed into the multiple sub-problems, one for each file. An investigation is made on the file placement problem, with the

Ph.D.

objective of minimizing the overall storage, migration, updating and operational costs on the system. By showing that the file placement problem and the facility location problem are isomorphic, many results derived in one problem can be applied to solve the other problem. Further, some results derived in one problem can be shown to be weaker than the corresponding results derived in the other problem. The last two areas of study are related to the distributed scheduling of tasks on distributed systems and the design of the necessary hardware support for data management. The task scheduling problem for a distributed system is shown to be NP-complete. However, an optimal average algorithm is developed for a restricted class which minimizes the expected completion time for a set of random requests. In the hardware support issue, the design of an associative memory which is capable of equality, proximity, threshold and extremum searches is investigated. The complexity of the design is 17 gates per cell. Its extensions to the design of associative sequential memories and data base machines are developed.

#### ACKNOWLEDGEMENT

The author would like to express his sincere gratitude to a number of individuals for their help in the research and preparation of this dissertation. Special thanks is due to Professor C. V. Ramamoorthy who was his thesis supervisor and the dissertation committee chairman. Throughout the years, Professor Ramamoorthy has been a constant source of advice, guidance, support and encouragement. He was and will be an ideal for the author to follow. Without his support, none of these would have been possible.

The author would also like to thank Professors D. Ferrari and I. Adler for reading the thesis, providing many helpful and valuable advice and encouragement, and serving on the thesis committee. Special thanks are also due to Miss Y. W. Ma, for reading and typing part of the draft and criticizing on the research. She has also been a source of spiritual support and encouragement througout these years. In addition, his colleagues, Messers F. Bastani, F. Ho, G. Ho, J. Favaro, C. Jen, T. Krishnarao, F. Leung, R. Mok, C. Nam, H. H. So and K. Wu are thanked for providing many helpful comments and a friendly environment for research.

He also wants to thank the Ballistic Missile Defense, the Army Research Office and the National Science Foundation for its support through contracts DASG-60-77-C-0138, DAAG29-78-G-0189 and grants MCS-77-27293, MCS-77-28361. Messers C. R. Vick and J. E. Scalf are also thanked for their many helpful discussions.

Finally and most importantly, the author wishes to thank his parents in Hong Kong for their unselfish and devoted support, both spiritually and finally.

This thesis was typed on a DEC VAX 11/780 computer supported by NSF grant MCS78-07291.

i

# TABLE OF CONTENTS

•

| Chapter | 1 INTRODUCTION 1                                       |

|---------|--------------------------------------------------------|

| 1.1     | What is a Distributed Data Base 1                      |

| 1.2     | Issues in Designing Data Base Systems 3                |

|         | 1.2.1 Issues in Logical Organization 4                 |

|         | 1.2.2 Issues in Architecture                           |

|         | 1.2.3 Issues in Operational Control                    |

|         | 1.2.4 Issues in Evolution                              |

| 1.3     | Architecture of the System supporting a DDB 16         |

| 1.4     | Objectives and Contributions of the Research           |

|         | 1.4.1 Problem Statement 22                             |

|         | 1.4.2 Approach                                         |

|         | 1.4.3 Contributions of this Research                   |

| Chapter | 2 QUERY DECOMPOSITION ON A                             |

| DIST    | RIBUTED RELATIONAL DATA BASE 28                        |

| 2.1     | Queries on a Relational DB                             |

| 2.2     | The Placements of Relations on a DDB                   |

| 2.3     | Cost Reduction on the Placements of Relations on a DDB |

|         | by utilizing Redundant Information 40                  |

| 2.4     | A Numerical Example to illustrate the Use of Redundant |

|         | Information on a DDB 49                                |

| 2.5     | Cost Reduction on the Placements of Relations on a DDB |

|         | by File Partitioning                                   |

| 2.6     | A Numerical Example to Illustrate the Use of File      |

|         | Partitioning on a DDB                                  |

PAGE

| 2.7 Cost Reduction on the Placement of Relations on a DDB by   |

|----------------------------------------------------------------|

| utilizing Redundant Information and File Partitioning          |

| 2.8 A Numerical Example to illustrate the use of Additional    |

| Redundant Information and File Partitioning on a DDB           |

| 2.9 Conclusion                                                 |

| Chapter 3 THE PLACEMENT AND MIGRATION OF MULTIPLE COPIES       |

| OF A FILE ON A DCS                                             |

| 3.1 Introduction                                               |

| 3.2 Definition of the Problem                                  |

| 3.3 Motivations for File Placement and Migration               |

| 3.4 Previous Work on the File Allocation Problem               |

| 3.5 Previous Work on the Single Commodity Warehouse            |

| Location Problem                                               |

| 3.6 The Isomorphism between File Allocation and Single         |

| Commodity Warehouse Location                                   |

| 3.7 Implications of the Isomorphism between the FAP            |

| and the SCWLP                                                  |

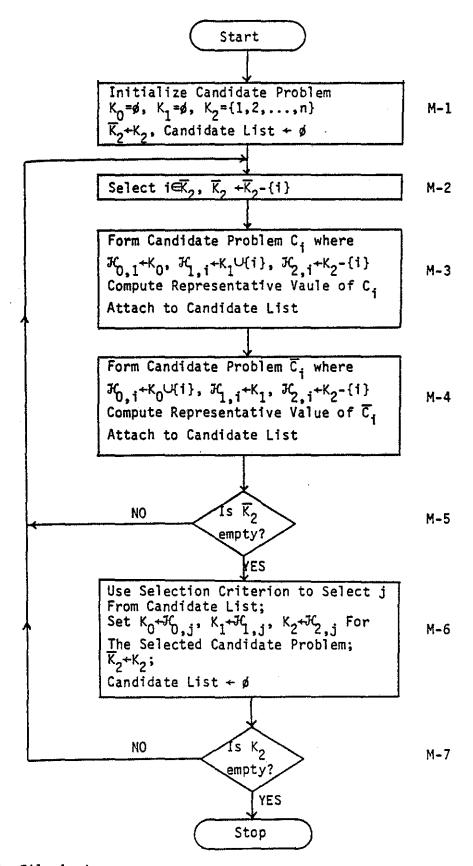

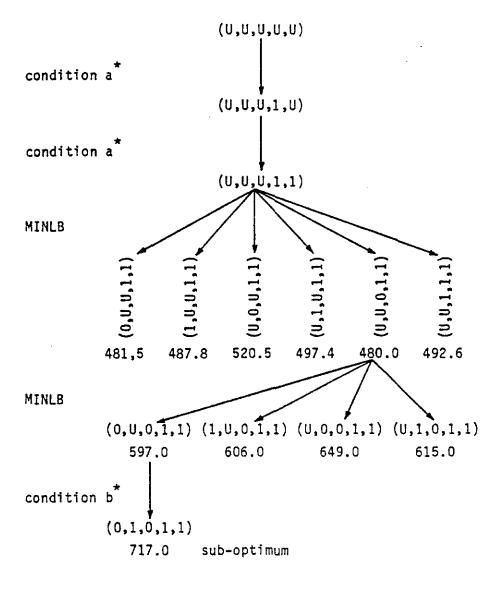

| 3.8 A Heuristic for the FAP - Algorithm 3.1                    |

| 3.9 DFAP - The Migration of Files on a DCS 103                 |

| 3.10 Conditions to reduce the Complexity of DFAP 106           |

| 3.10.1 The Problem of selecting the Times for Migration        |

| is NP-Complete 106                                             |

| 3.10.2 Criteria for initiating a Migration                     |

| 3.11 Conclusion 114                                            |

| Chapter 4 TASK SCHEDULING ON DISTRIBUTED COMPUTER SYSTEMS 116  |

| 4.1 Introduction 116                                           |

| 4.2 A Model for the scheduling of Tasks on Distributed Systems |

| 4.2.1 The Model 119                                               |

|-------------------------------------------------------------------|

| 4.2.2 Assumptions which allow the Task Scheduling Problem         |

| to be simplified125                                               |

| 4.3 NP-completeness of the Task Scheduling Problem                |

| 4.4 The Restricted Model - An Optimal Algorithm for               |

| scheduling Requests on an Interleaved Memory System               |

| 4.4.1 Requirements for the Design of a Primary Memory 137         |

| 4.4.2 Characteristics of the Access Sequence of a                 |

| Pipelined Processor 139                                           |

| 4.4.3 Previous work on the Study of Interleaved Memories          |

| 4.4.4 The Organizations of Primary Memory for a Pipelined         |

| Processor 145                                                     |

| 4.4.5 Optimality of the MWFMF Scheduling Algorithm 157            |

| 4.4.6 Embedded Markov Chain Technique 172                         |

| 4.4.7 Simulation Technique 178                                    |

| 4.4.7.1 Simulation Results                                        |

| 4.4.7.2 Application of Multiple Linear Regression                 |

| to obtain a Closed Form Formula182                                |

| 4.4.8 Effects of separating the Instruction and the Data Area 193 |

| 4.4.9 Degradation in Performance due to Dependencies              |

| 4.4.9.1 The Model used to estimate the Performance due            |

| to Dependencies196                                                |

| 4.4.9.2 Computation of Degradation in Performance 199             |

| 4.4.10 Some Final Remarks about the Design of                     |

| Interleaved Memories                                              |

| 4.5 A Heuristic for the scheduling of Tasks on the General Model  |

| 4.6 Conclusion 216                                                |

|                                                                   |

.

| Chapter 5 HARDWARE SUPPORT FOR DATA MANAGEMENT ON DISTRIBUTED  |

|----------------------------------------------------------------|

| COMPUTER SYSTEMS 218                                           |

| 5.1 Introduction                                               |

| 5.2 A Design of a Fast Cellular Associative Memory for Ordered |

| Retrieval                                                      |

| 5.2.1 Previous Work                                            |

| 5.2.2 Symbols used in the Design                               |

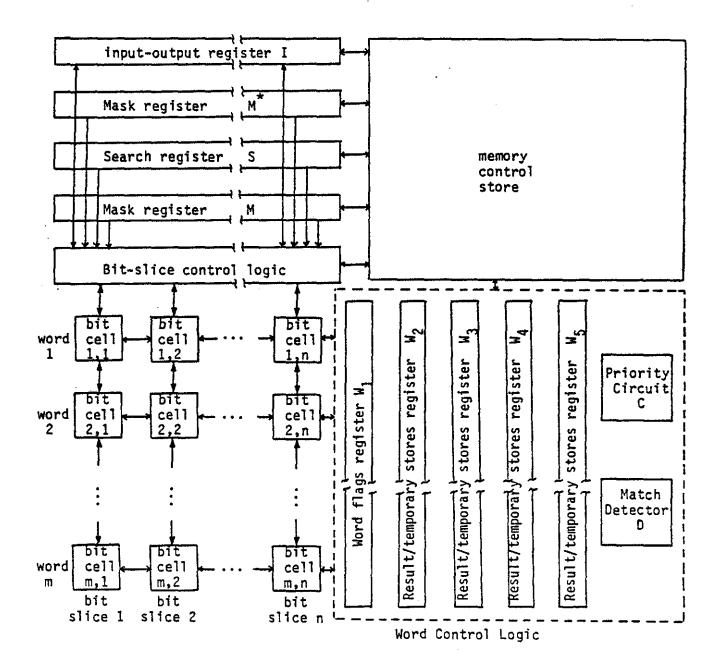

| 5.2.3 Basic Associative Memory Organization 224                |

| 5.2.4 Definition of Search Operations                          |

| 5.2.5 Algorithms and Implementations of Basic Searches         |

| 5.2.5.1 Mode A: Equality-Proximity-Threshold Search Mode. 229  |

| 5.2.5.2 Mode B: Least Value Search Mode                        |

| 5.2.5.3 Mode C: Greatest Value Search Mode                     |

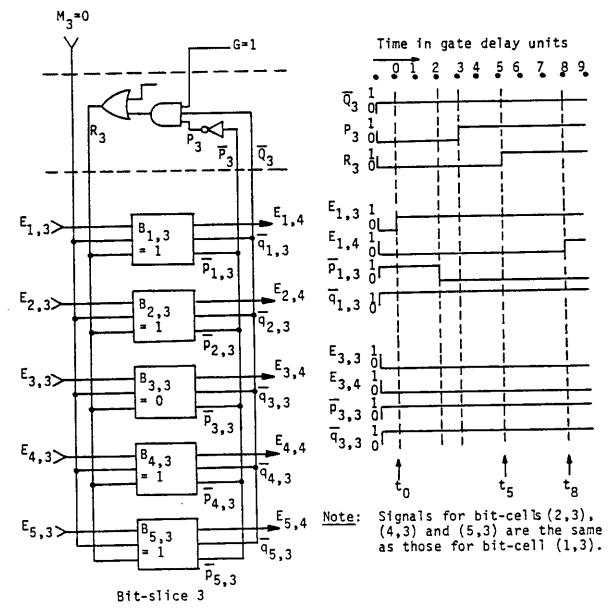

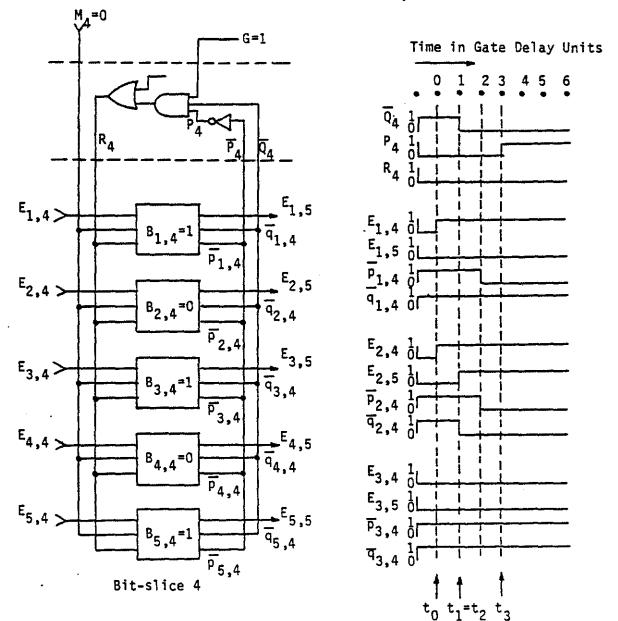

| 5.2.6 Ordered Retrieval 242                                    |

| 5.2.7 Some Speed-up Techniques 244                             |

| 5.2.8 Issues and Limitations                                   |

| 5.2.8.1 LSI Implementation                                     |

| 5.2.8.2 Manufacturing Defects                                  |

| 5.2.8.3 Modular Expansion                                      |

| 5.2.8.4 Multiple Match Resolution                              |

| 5.2.9 Comparisons with other Methods of Ordered Retrieval      |

| 5.3 Data Base Machines                                         |

| 5.3.1 Introduction                                             |

| 5.3.2 Issues in the Design of Data Base Machines               |

| 5.3.3 Classification of Data Base Machines                     |

| 5.3.4 Extension of the Associative Memory Design to            |

| Sequential Memories                                            |

|                                                                |

•

| 5.4 Conclusion                                                | 80 |

|---------------------------------------------------------------|----|

| Chapter 6 CONCLUSION 2                                        | 82 |

| Appendix A THE ISOMORPHISM BETWEEN PROCESS ALLOCATION PROBLEM |    |

| AND THE SINGLE COMMODITY QUADRATIC ASSIGNMENT PROBLEM 2       | 85 |

| Appendix B THE LINEAR PROGRAMMING LOWER BOUND OF A CANDIDATE  |    |

| PROBLEM 2                                                     | 87 |

| Appendix C THE EXPECTED VALUE OF A CANDIDATE PROBLEM          | 89 |

| Appendix D BIBLIOGRAPHY 2                                     | 91 |

-

•

# LIST OF FIGURES

.

| Figure 1.1 | Classification of Issues in Distributed Data Base Systems                     | 5  |

|------------|-------------------------------------------------------------------------------|----|

| Figure 1.2 | Architecture of a DDB System                                                  | 10 |

| Figure 1.3 | The Density Growth of Large Scale Integrated Circuits                         | 11 |

| Figure 1.4 | The Exponential Growth of CPU Speed                                           | 13 |

| Figure 1.5 | Availability of Memory Technologies                                           | 17 |

| Figure 1.6 | Storage Hierarchy                                                             | 19 |

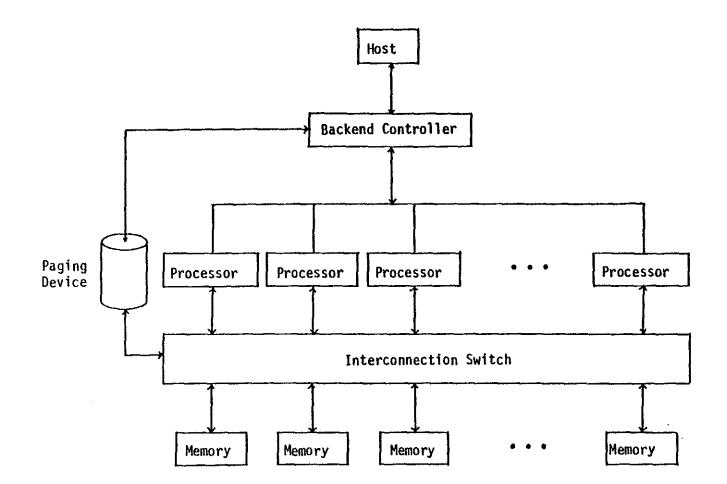

| Figure 1.7 | Architecture of a Data Base Machine                                           | 20 |

| Figure 1.8 | Relationships among Various Data Management Issues                            | 25 |

| Figure 2.1 | Relations S and SP (not all domains are shown)                                | 29 |

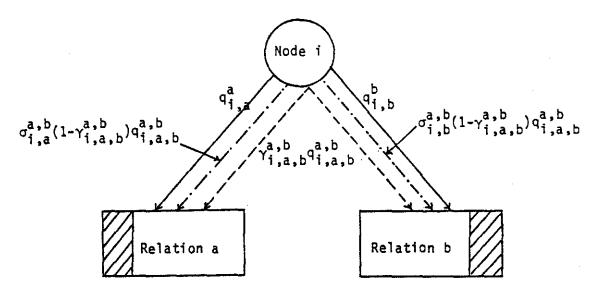

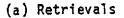

| Figure 2.2 | Retrieval and Update Rate on a 2-Relation DDB from Node i                     | 34 |

| Figure 2.3 | Relations S and SP with (S.s#=SP.s#) information                              |    |

|            | compiled into the Relations                                                   | 41 |

| Figure 2.4 | Retrieval and Update Rates on a 2-relations DDB from Node                     |    |

|            | i using Additional Redundant Information                                      | 45 |

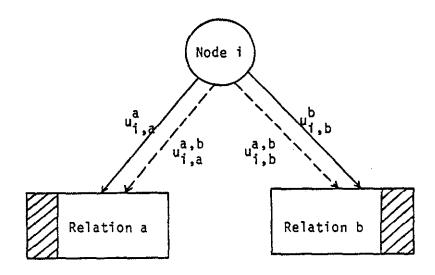

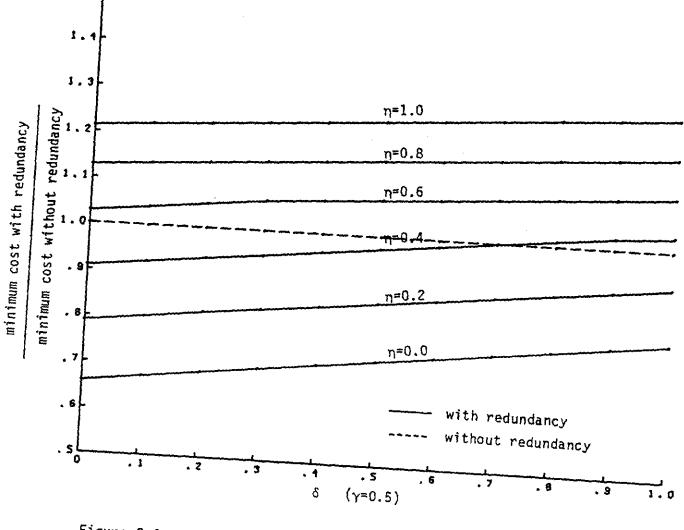

| Figure 2.5 | A Plot of Cost Ratio w.r.t. $\gamma$ for Various Values of $\delta$           |    |

|            | under the use of Redundancy                                                   | 51 |

| Figure 2.6 | A Plot of Cost Ratio w.r.t. $\eta$ for Various Values of $\delta$             |    |

|            | under the use of Redundancy                                                   | 52 |

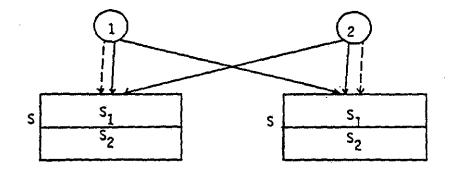

| Figure 2.7 | The Retrievals and Updates on a DDB (2 nodes) with and                        |    |

|            | without File Partitioning                                                     | 54 |

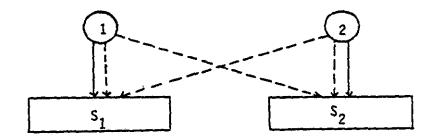

| Figure 2.8 | A Plot of Cost Ratio w.r.t. $fu^1$ for Various Values                         |    |

|            | of $fu^2$ under File Partitioning                                             | 60 |

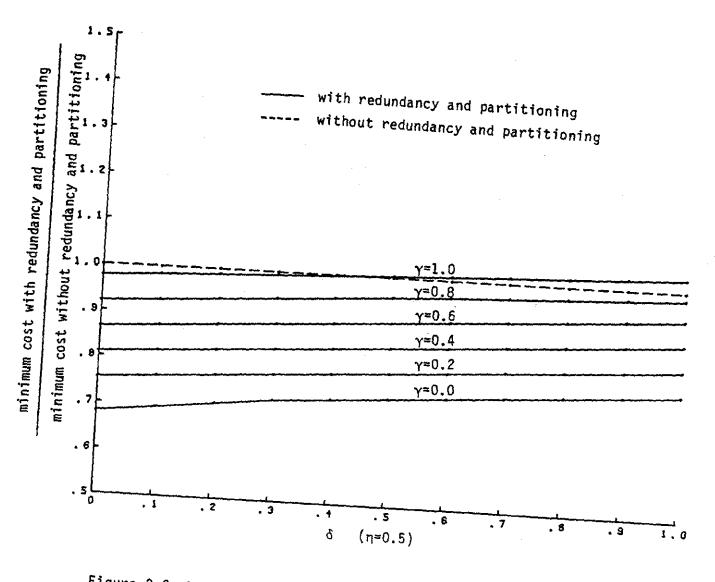

| Figure 2.9 | A Plot of Cost Ratio w.r.t. $\gamma$ for Various Values of $\delta$ under the |    |

|            | use of Redundancy and Partitioning $(fu^1=fu^2=0.75)$                         | 35 |

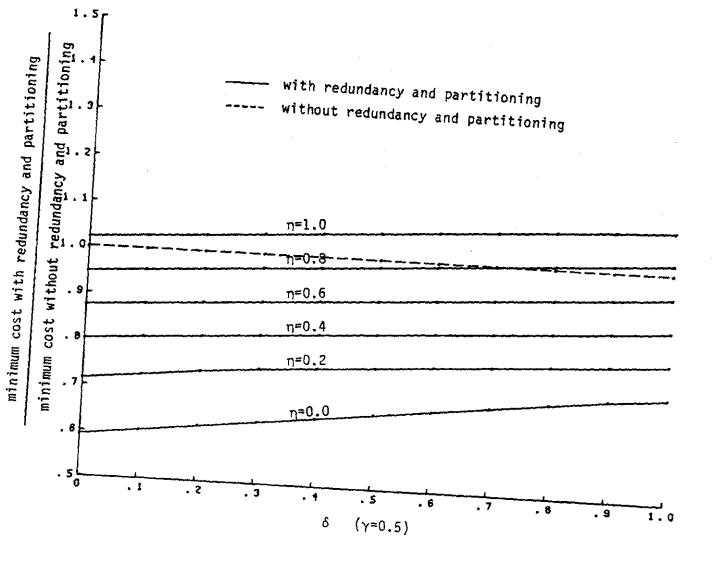

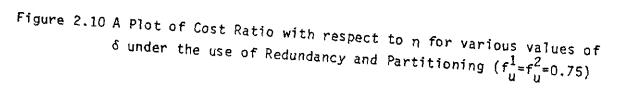

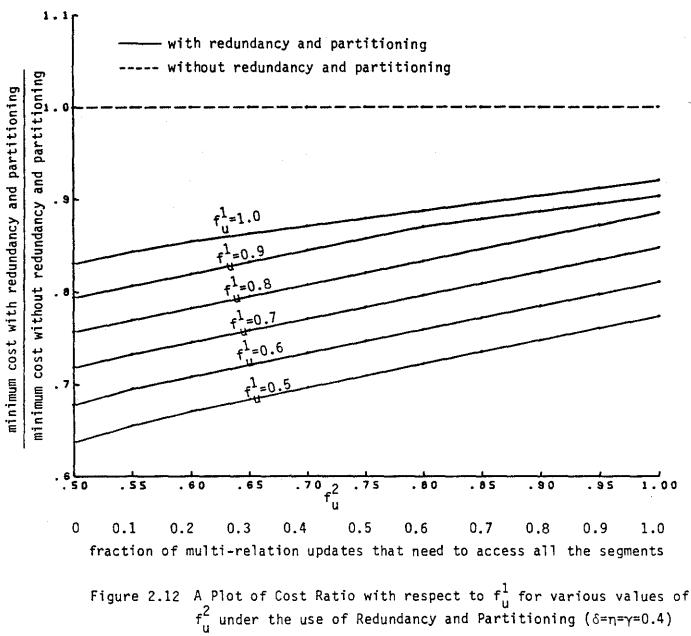

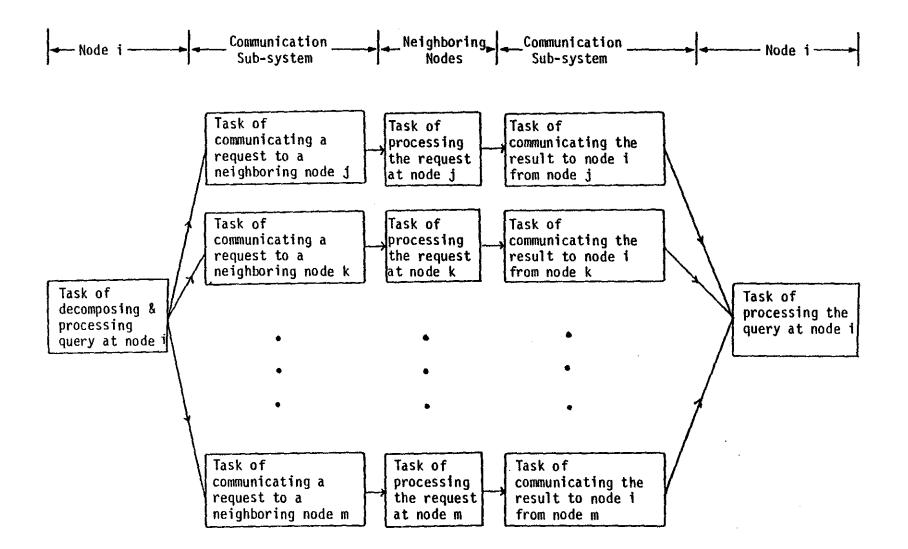

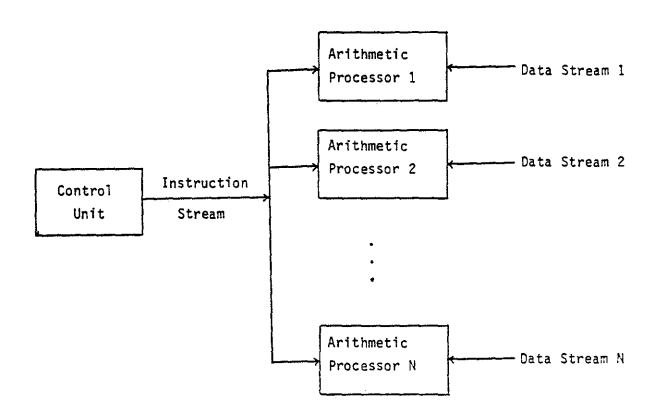

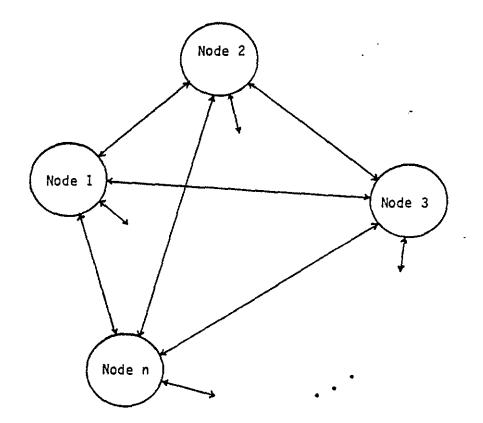

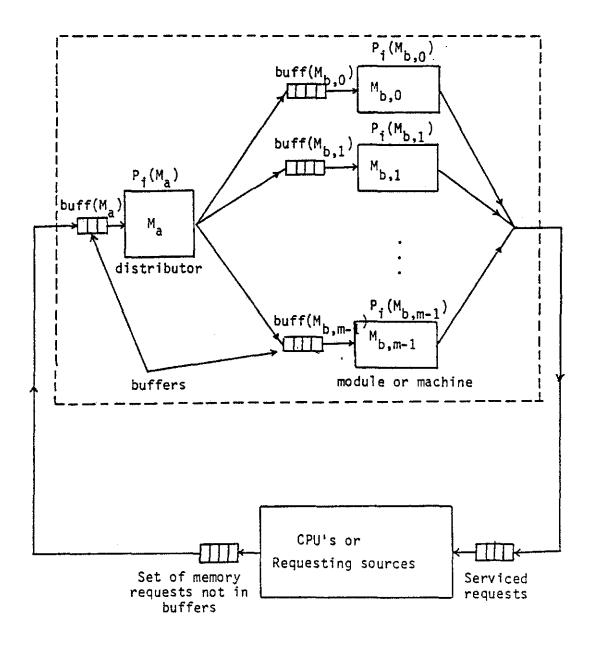

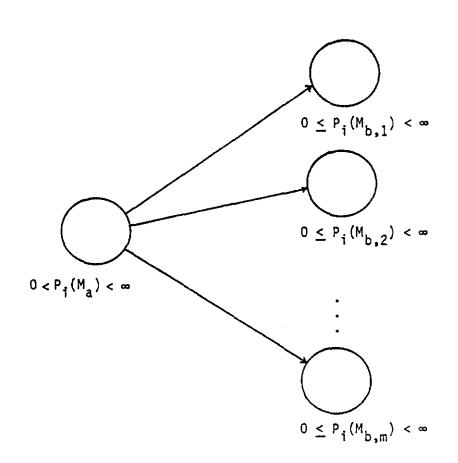

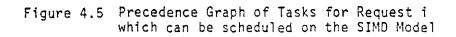

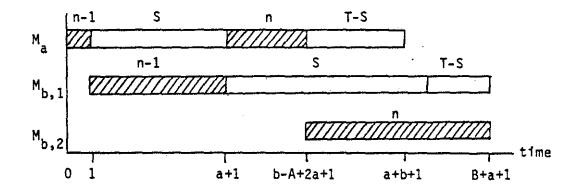

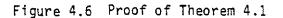

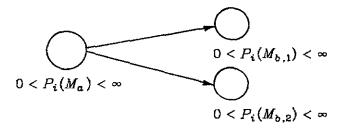

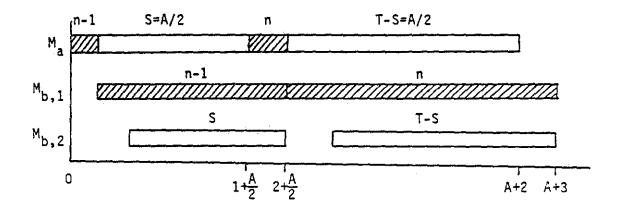

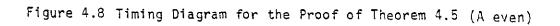

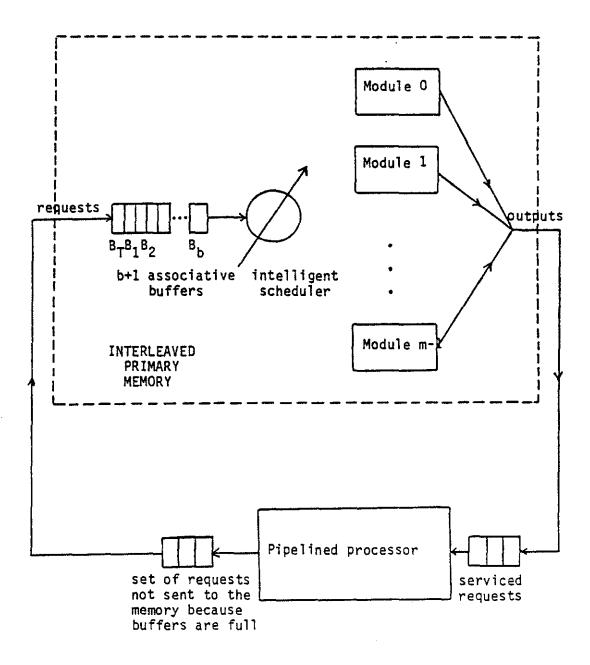

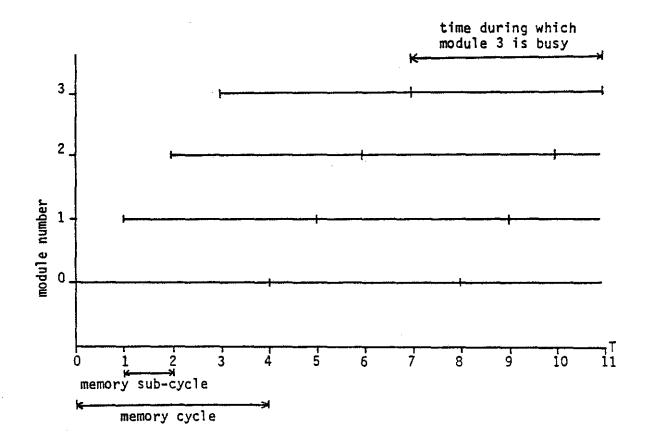

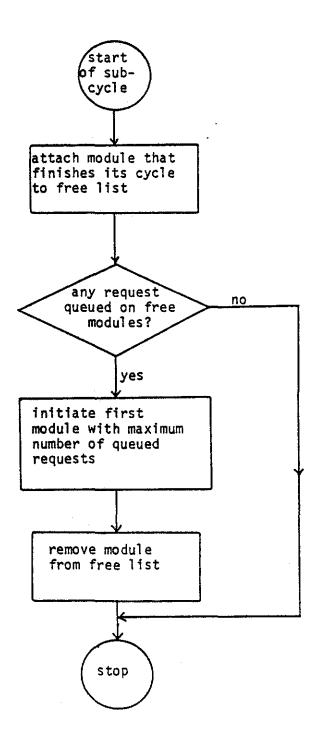

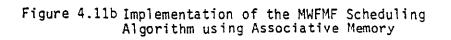

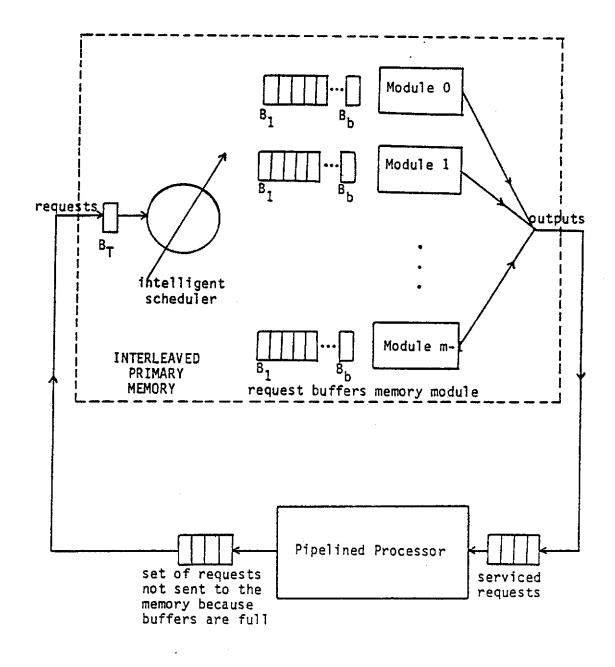

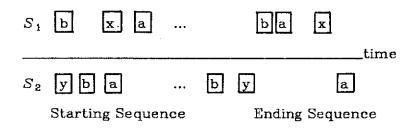

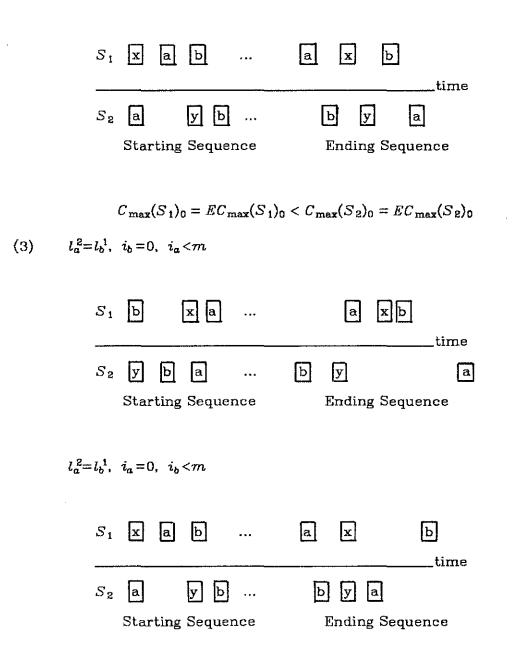

Figure 2.10 A Plot of Cost Ratio w.r.t.  $\eta$  for Various Values of  $\delta$  under the Figure 2.11 A Plot of Cost Ratio w.r.t.  $fu^1$  for Various Values of  $fu^2$  under Figure 2.12 A Plot of Cost Ratio w.r.t.  $fu^1$  for various values of  $fu^2$  under Figure 4.1 Task Precedence Graph for the Processing of a Query which requires the Use of Geographically Distributed Files ...... 118 Figure 4.2 Model of an SIMD Computer System ...... 120 Figure 4.3 Conceptual Model of a DCS ..... 121 Figure 4.4 An SIMD Model for Task Scheduling on a DCS ...... 123 Figure 4.5 Precedence Graph of Tasks for Request i which can be scheduled on the SIMD Model ..... 124 Figure 4.6 Proof of Theorem 4.1 ..... 130 Figure 4.7 Timing Diagram for the Proof of Theorem 4.2...... 132 Figure 4.9 Organization I - A Model of Interleaved Memories with a Figure 4.10 A Gantt Chart to illustrate the Operation of the Interleaved Memories in Staggered Cycles (m=4) ..... 148 Figure 4.11 MWFMF Scheduling Algorithm - Algorithm 4.3 ...... 151,2 Figure 4.12 Organization II - A Model of Interleaved Memories with

viii

×,

| Multiple Request Queues 154                                                |

|----------------------------------------------------------------------------|

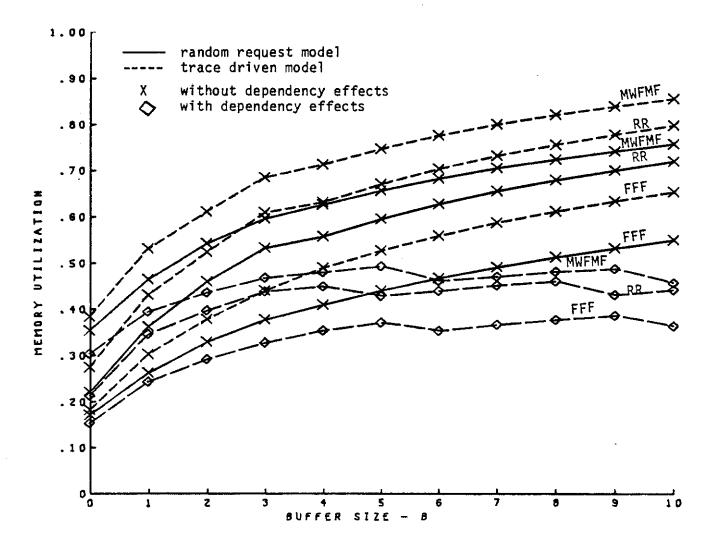

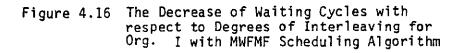

| Figure 4.13 The Improvement of Average Memory Utilization with Buffer      |

| Size for Org. I (m=8) 188                                                  |

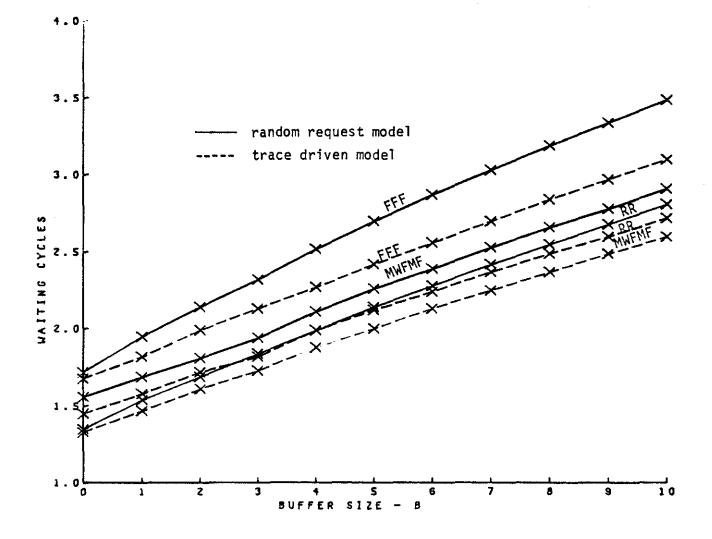

| Figure 4.14 The Increase of Average Waiting Cycles with Buffer Size        |

| for Org. I (m=8) 189                                                       |

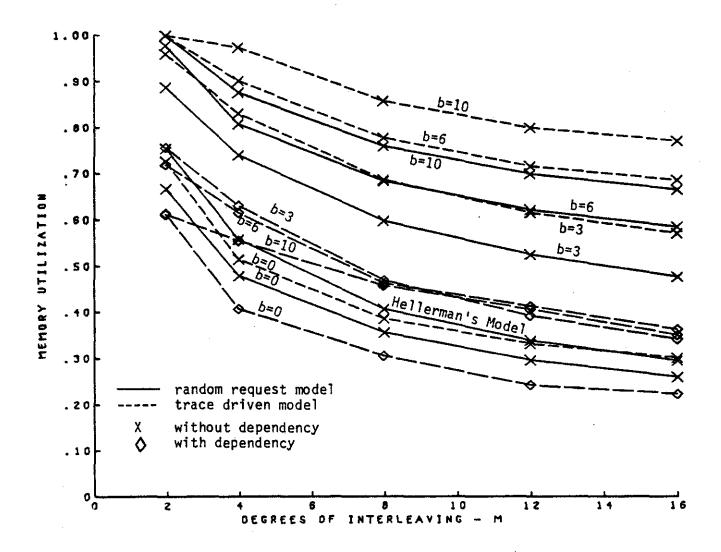

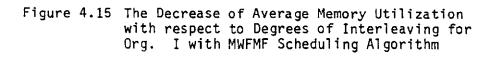

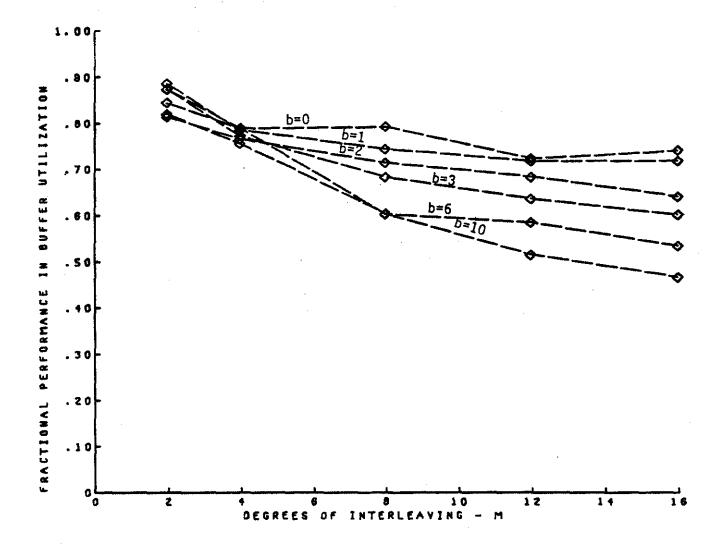

| Figure 4.15 The Decrease of Average Memory Utilization w.r.t. Degrees      |

| of Interleaving for Org. I with MWFMF Scheduling Algorithm 190             |

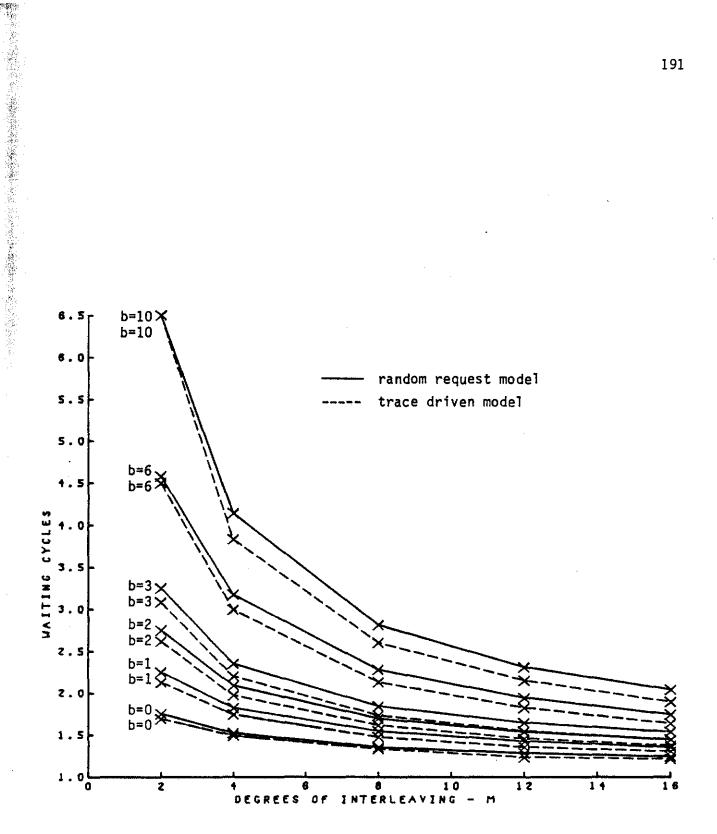

| Figure 4.16 The Decrease of Waiting Cycles w.r.t. Degrees of Inter-        |

| leaving for Org. I with MWFMF Scheduling Algorithm 191                     |

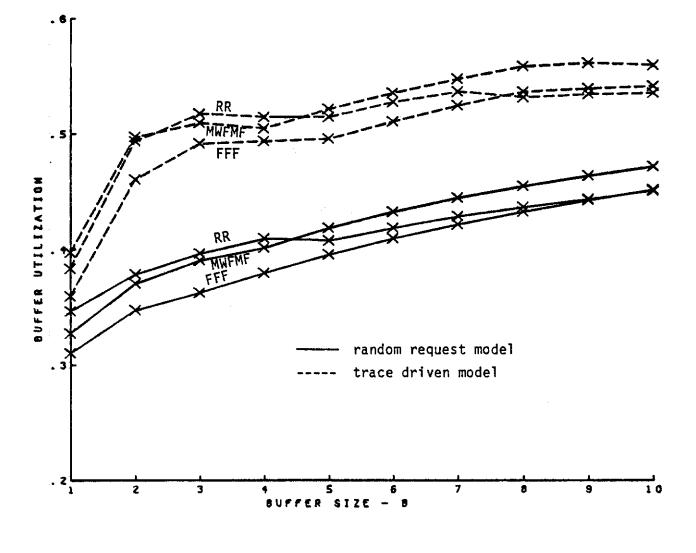

| Figure 4.17 The Average Buffer Utilization for Org. II (m=8) 192           |

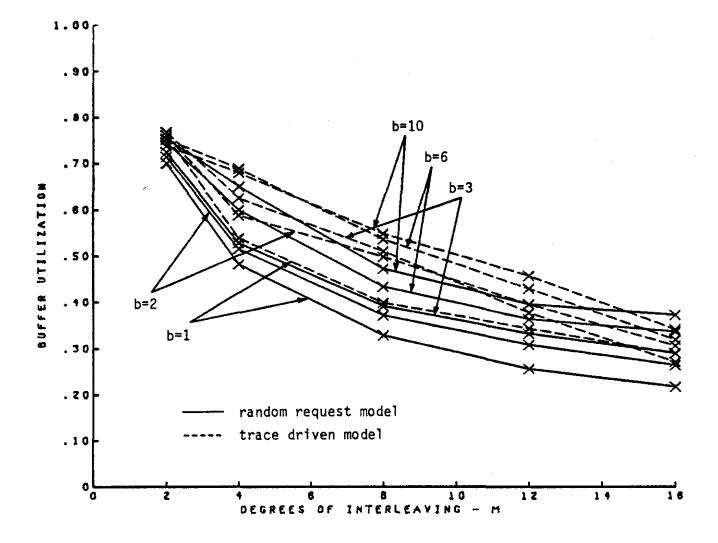

| Figure 4.18 The Average Buffer Utilization vs. the Degrees of Inter-       |

| leaving for Org. II with MWFMF Scheduling Algorithm (m=8) 194              |

| Figure 4.19 Model of CPU-Memory used for Estimation of the Effects         |

| of Dependency 198                                                          |

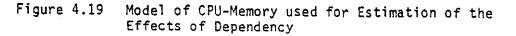

| Figure 4.20 Histogram showing the Statistics of Dependent Events           |

| in Traces used 200                                                         |

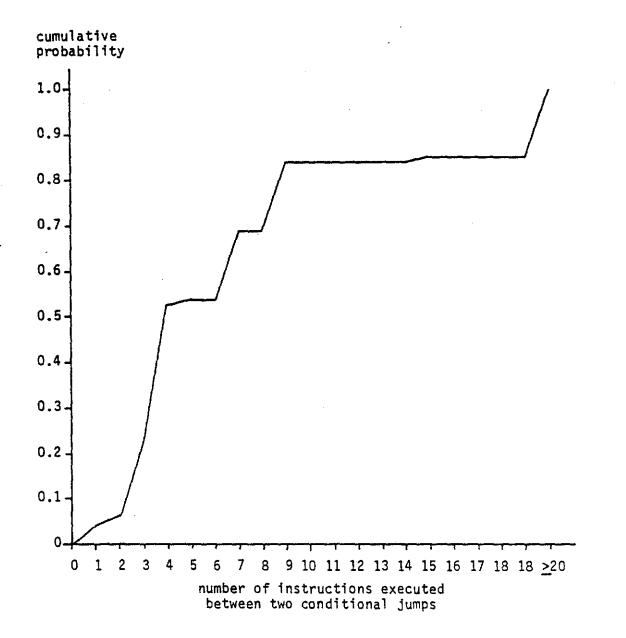

| Figure 4.21 Graph showing the Cumulative Probability of Number of          |

| Instructions executed between 2 Conditional Jumps 201                      |

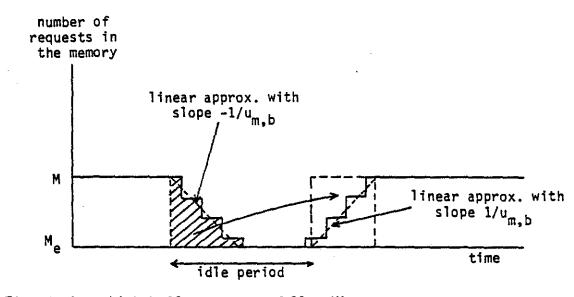

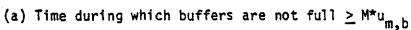

| Figure 4.22 The Variation of the Number of Requests in the Buffers 202     |

| Figure 4.23 Buffer Utilization under Dependency for Org. I with a          |

| MWFMF Algorithm (Trace Driven Simulations)                                 |

| Figure 4.24 Simulation Results for Algorithm 4.4 using 1000 Samples        |

| of 7 Randomly Generated Jobs (m=2, p=2)                                    |

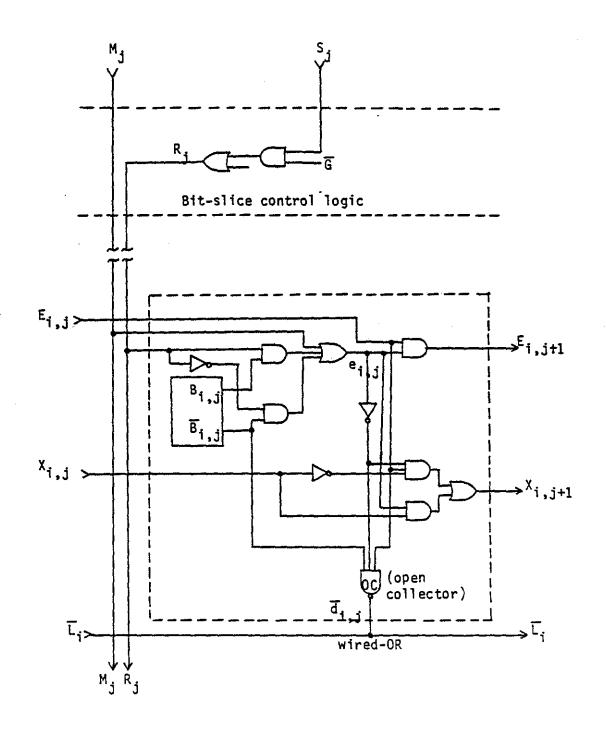

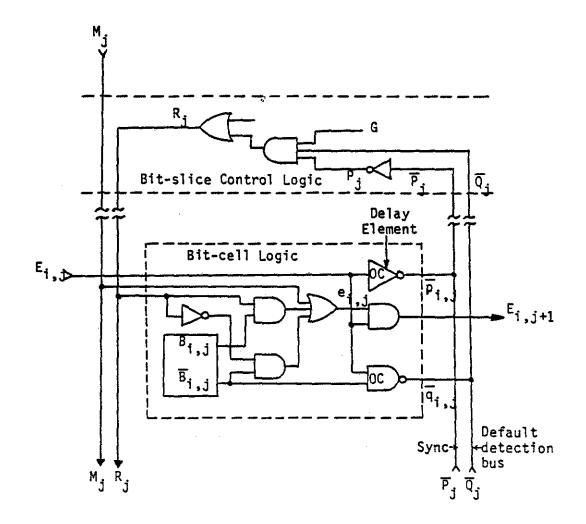

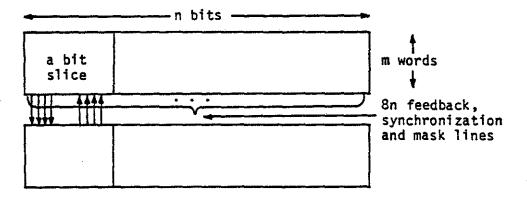

| Figure 5.1 Cellular Logic Associative Memory Block Diagram                 |

| Figure 5.2 Bit-cell with Equality, Greater-than, Less-than and             |

| Proximity Capability for Mode A Operation                                  |

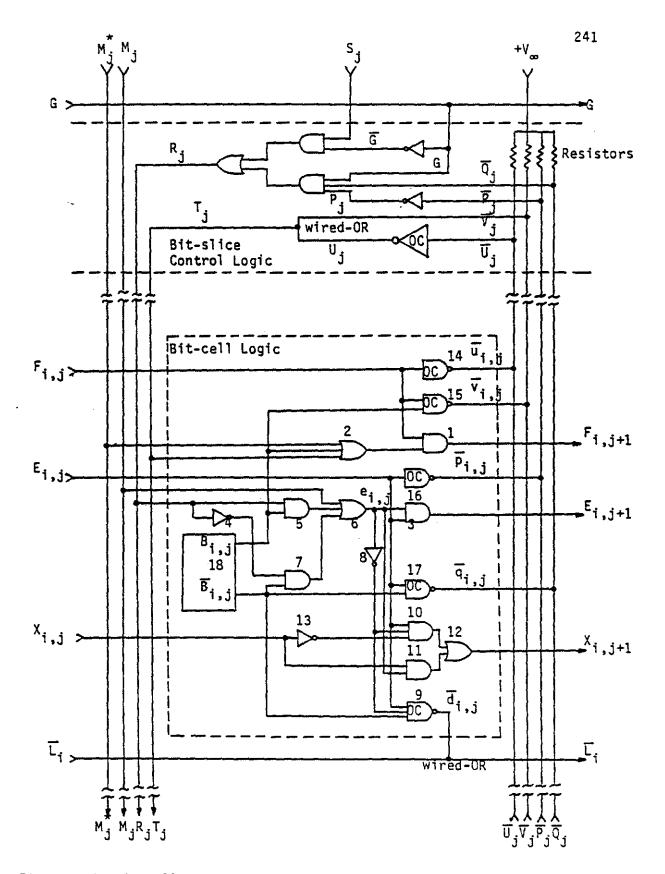

| Figure 5.3 Bit-cell with Least Value Search Logic for Mode B Operation 235 |

| Figure 5.4  | Bit-cell for Simultaneous Ascending Order Retrieval and Descend | ing |

|-------------|-----------------------------------------------------------------|-----|

|             | Order Retrieval or Equality-Threshold-Proximity Searches        | 241 |

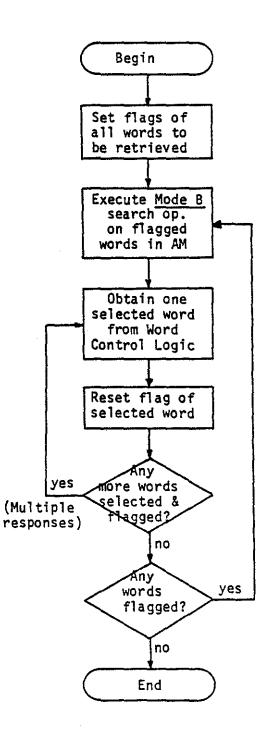

| Figure 5.5  | Flow Chart for Ascending Order Retrieval                        | 243 |

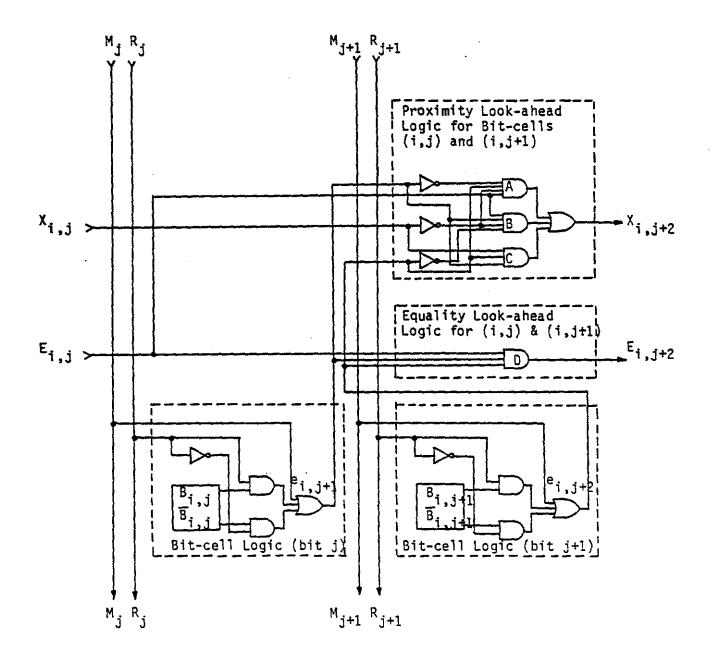

| Figure 5.6  | Bit-cell j and j+1 of word i with Equality-Proximity Search     |     |

|             | and Lookahead Logic                                             | 246 |

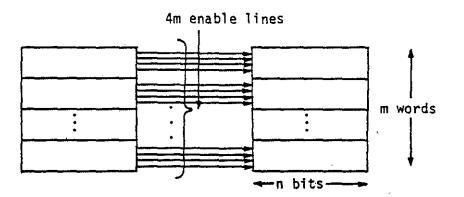

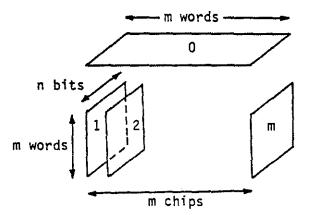

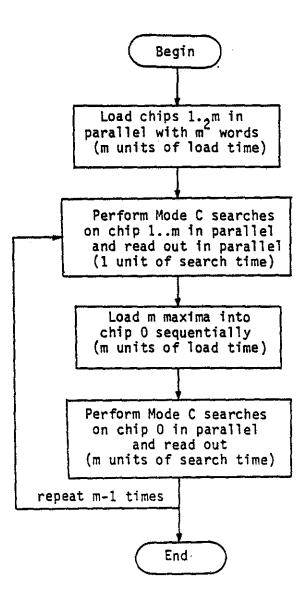

| Figure 5.7  | Modular Extension for Proposed Associative Memory               | 256 |

| Figure 5.8  | Flow Chart for Ascending Order Retrieval of $m^2$ words         |     |

|             | in a 3-dimensional Associative Memory [see Fig. 5.7c]           | 257 |

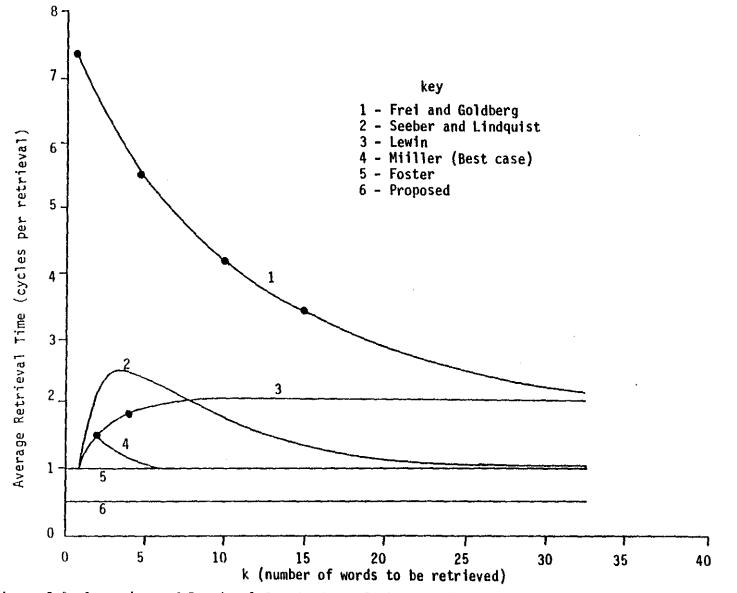

| Figure 5.9  | Comparison of Retrieval Speeds for a 5 bit Tag with             |     |

|             | k Words Flagged                                                 | 264 |

| Figure 5.10 | Backend Systems using Conventional Mini-computers               | 269 |

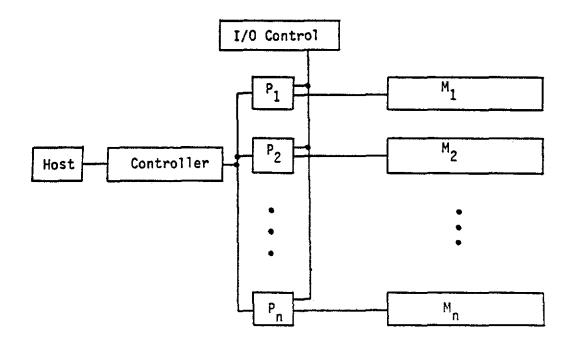

| Figure 5.11 | Intelligent Controllers - Cellular Logic                        | 271 |

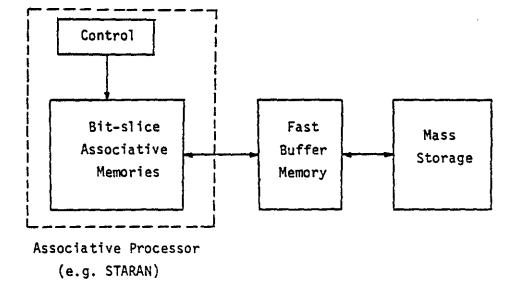

| Figure 5.12 | 2 Intelligent Controllers - Associative Memories                | 274 |

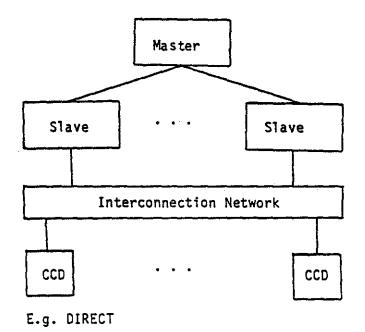

| Figure 5.13 | B Intelligent Controllers - MIMD Architecture                   | 275 |

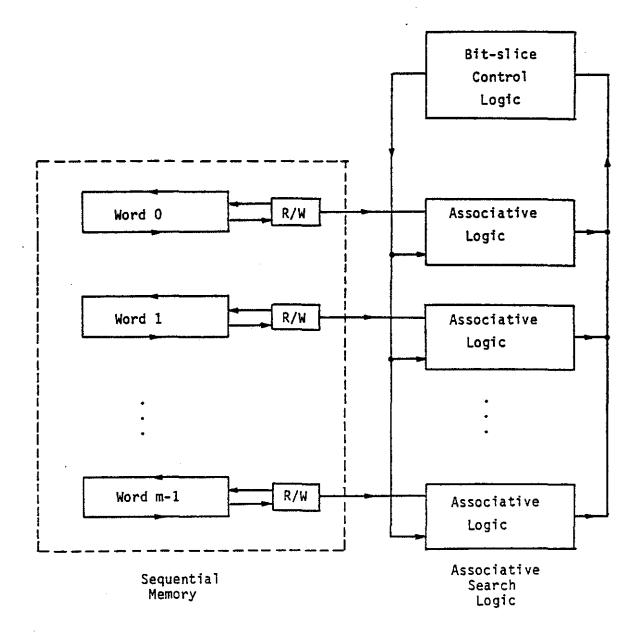

| Figure 5.14 | Associative Sequential Memory                                   | 278 |

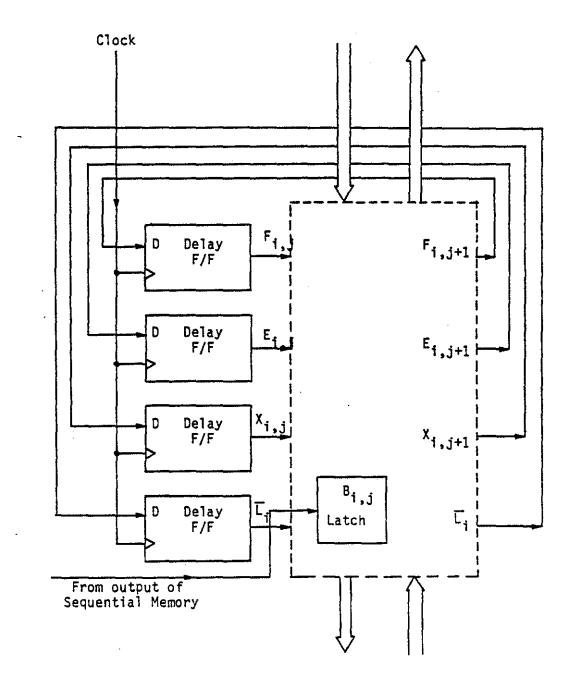

| Figure 5.15 | Associative Logic for Associative Sequential Memory             | 279 |

|             |                                                                 |     |

,

.

# LIST OF TABLES

•

# PAGE

| Table 1.1 Typical Ballistic Missile Defense Data Base Processing               |

|--------------------------------------------------------------------------------|

| Requirements in a Centralized Environment                                      |

| Table 1.2 Typical Values for LSI Semiconductor RAM's (1978)       12           |

| Table 3.1 Examples of Communication Costs on Telenet Data                      |

| Communication Network (July 1, 1978)                                           |

| Table 3.2 A Summary of the Previous Work in File Placement/Migration 76        |

| Table 3.3 Mapping between the Defined Notations in this Thesis                 |

| and Casey's Notations                                                          |

| Table 3.4 Mapping between the (D)FAP and the SC(D)WLP                          |

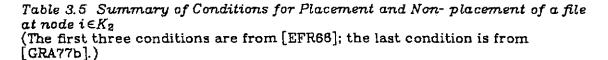

| Table 3.5 Summary of Conditions for Placement and Non-Placement                |

| of a file at Node $i \in K_2$                                                  |

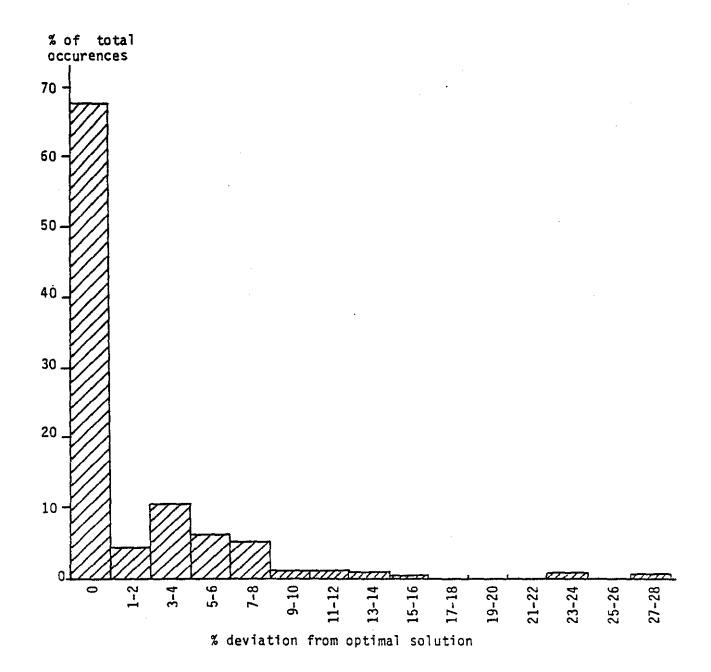

| Table 3.6 % Deviations of File Allocation Heuristic from Optimal Solutions 101 |

| Table 3.7 Execution Time of Heuristic in Seconds on the CDC 6400 102           |

| Table 4.1a Simulation Results for Org. I with RR Algorithm 179                 |

| Table 4.1b Simulation Results for Org. I with FFF Algorithm                    |

| Table 4.1c Simulation Results for Org. I with MWFMF Algorithm 181              |

| Table 4.2a Simulation Results for Org. II with RR Algorithm 183                |

| Table 4.2b Simulation Results for Org. II with FFF Algorithm 184               |

| Table 4.2c Simulation Results for Org. II with MWFMF Algorithm 185             |

| Table 4.3 Coefficients of 3rd Order Polynomial Regression of                   |

| Organizations I and II under MWFMF Scheduling Algorithm 186                    |

| Table 4.4 Comparison between Merged and Separated Instruction-Data             |

| Areas for Org. I - Trace Driven Simulations                                    |

| Table 4.5 Comparison between Merged and Separated Instruction-Data             |

|           | Areas for Org. II - Trace Driven Simulations               | 195 |

|-----------|------------------------------------------------------------|-----|

| Table 5.1 | A Comparison Table for Ordered Retrieval Schemes           | 262 |

| Table A-1 | Mapping between Stone's Process Allocation Problem and the |     |

|           | Single Commodity Quadratic Assignment Problem              | 286 |

#### 1. INTRODUCTION

The recent advances in large scale integrated logic and communication technology, coupled with the explosion in size and complexity of the application areas, have led to the design of distributed architectures. Basically, a *Distributed Computer System (DCS)* is considered as an interconnection of digital systems called *Processing Elements (PEs)*, each having certain processing capabilities and communicating with each other. This definition encompasses a wide range of configurations from an uniprocessor system with different functional units to a multiplicity of general purpose computers (e.g. ARPANET). In general, the notion of "distributed systems" varies in character and scope with different people [RAM76]. So far, there is no accepted definition and basis for classifying these systems. In this thesis, we limit our discussion to a class of DCS's with an interconnection of dedicated/shared, programmable, functional PEs and working on a set of jobs which may be related or unrelated.

#### **1.1 WHAT IS A DISTRIBUTED DATA BASE**

Due to the information explosion and the need for more stringent requirements, the design of efficient coordination schemes for the management of data on a DCS is a very critical problem. To indicate the amount of data processed, the typical data base processing requirements for a ballistic missile defense system [DDP78], operating in a centralized environment are shown in Table 1.1. In order to manage the data on a computer system (centralized or distributed) and satisfy all the requirements, systematic techniques must be developed so that the system can be realized in a cost-effective way.

Data on a DCS are managed through a *Data Base (DB)*, which is a collection of stored operational data used by the application systems of some particular enterprise [DAT77, FRY76]. A *Distributed Data Base (DDB)* can be thought of as objective of minimizing the overall storage, migration, updating and operational costs on the system. By showing that the file placement problem and the facility location problem are isomorphic, many results derived in one problem can be applied to solve the other problem. Further, some results derived in one problem can be shown to be weaker than the corresponding results derived in the other problem. The last two areas of study are related to the distributed scheduling of tasks on distributed systems and the design of the necessary hardware support for data management. The task scheduling problem for a distributed system is shown to be NP-complete. However, an optimal average algorithm is developed for a restricted class which minimizes the expected completion time for a set of random requests. In the hardware support issue, the design of an associative memory which is capable of equality, proximity, threshold and extremum searches is investigated. The complexity of the design is 17 gates per cell. Its extensions to the design of associative sequential memories and data base machines are developed. programs, together with the sub-schema, collectively form the Data Base Management System [FRY76, BAC75]. The Data Base Management System allows data sharing among a community of users, while insuring the integrity of the data over time, and providing security against unauthorized access. It also provides the transparency of the data, in order to allow the data to be stored in different formats in different parts of the system. Finally, it provides an interface between the users and the system.

The data base can be classified according to how these components are put together. In [ASC74], two classifications are proposed, the first is based on the number of Data Base Management Systems in the network and the second is based on the centralization or decentralization of the file directory and the data. In [B0076], the DDB's are classified into two structures, partitioned data bases and replicated data bases. A partitioned data base is one that has been decomposed into physically separate units, and distributed across multiple nodes of a DCS. The partitioning will normally be based on the distribution of access requirements. In a replicated data base, all or part of the data base is replicated at multiple processing nodes. The amount of partitioning and replication depends on the architecture of the distributed system, the amount of traffic anticipated and other requirements such as reliability, security, etc.

# 1.2 ISSUES IN DESIGNING DISTRIBUTED DATA BASE SYSTEMS

The issues associated with the design of a DDB can be classified from an user's viewpoint or from a system designer's viewpoint. From an user's viewpoint, the users are concerned with the type of organization and controls which can give efficient and reliable operations and can satisfy their requirements. The users usually do not relate very closely other factors such as technology and architecture in their considerations. On the other hand, from a designer's viewpoint, the designers are more concerned with the architecture of

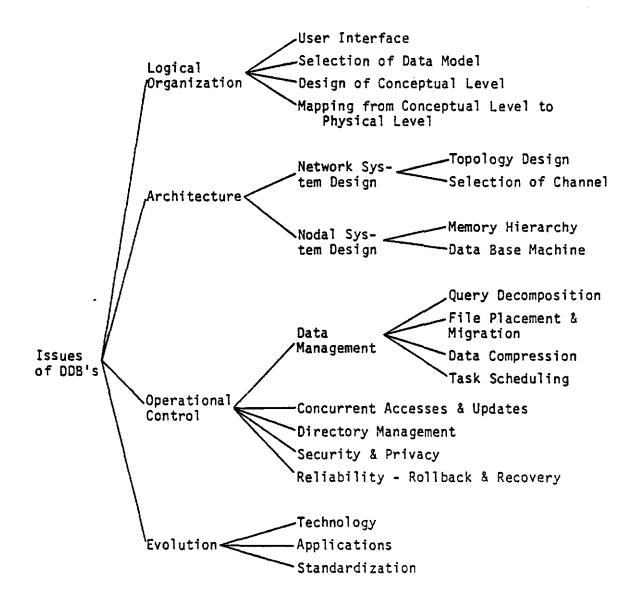

the system and its dependency on technology. However, the issues considered from both viewpoints are not independent and must be investigated jointly in the design of a DDB. We have therefore taken an integrated approach and have classified these issues into four categories. The classification is shown in Figure 1.1.

#### 1.2.1 Issues in Logical Organization

These issues are related to the user-system interface and can be classified as:

#### (A) User Interface

The user interface may be defined as a boundary in the system below which everything is invisible to the user [DAT77]. The function of this interface is to provide the users with an efficient and powerful query language and to help the users to manipulate the data in the DB. The query language must be powerful enough so that an entire set can be manipulated as a single object, instead of being restricted to one record at a time. The complexity of this interface depends on the required ease with which users wish to access the data and it directly governs the design of communication processors.

#### (B) Data Base Organization

A data base is generally organized in one or more of the data models: relational, hierarchical or network model, where a data model refers to a representation of the entire information content of the DB in a form that is somewhat abstract in comparison with the way in which data is physically stored [DAT77]. There are other models like the binary association model and the external set model which are not quite popular. Each user views the data base through an external model which may be one of the above data models. The data base should therefore be able to support multiple data models for different users and

to provide users with transparent accesses. The efficiency of a DDB is very much dependent on the type of organization since it affects the storage organization, access mechanisms and the communication requirements. The criteria for designing and selecting a model has not yet been well understood or established, nor is it likely to be established in the near future. The designers of a DDB are therefore confronted with two decisions: which data model to utilize and how to structure the data for a chosen model [SIL76]. Further, there is the problem of mapping the different external models onto the conceptual level.

## (C) Design of the Conceptual Level

The conceptual level is a level of indirection between the external level which consists of different data models and language interfaces and the internal level which consists of the physically stored data. The conceptual level actually maps the users' views onto physical data and is intended to provide a solid and enduring foundation for the total operation of the DDB. Its design depends on how the data are stored, the physical storage media, the number of different data models, the way that data are distributed on the DCS and other user requirements. It is important to construct a conceptual schema at a suitable level of abstraction in the design stage [DAT77]. Many of the techniques in artifical intelligence have been applied successfully in this design.

### 1.2.2 Issues in Architecture

## (A) Network System Design

The DCS is made up of nodal processors interconnected together through an interconnection network. There are many data base related issues associated with the design of network systems in addition to the design issues of efficient nodal systems. Among these are: the selection of network topology to support DDB requests; the selection of the channel type; the design of network control strategies; the design of communication processors, etc. Some of these issues have been studied in [RAM76, RAM79b].

# (B) Nodal System Design

The design of the nodal architecture to support a DDB is concerned with the design of fast storage sub-system whose function is to provide the nodal processor sub-system and users with fast retrievals and accesses to the stored data. The storage sub-system usually consists of a memory hierarchy that is divided into levels. These levels are made up of memory elements of varying speeds and the fastest level is interfaced to the processor sub-system. Further, intelligence have also been distributed to the various levels of the hierarchy. One such design is the data base machine [HSI77]. Issues like the selection of the number of levels and the size of each level of the memory hierarchy; the design of virtual memory for automatic file management; the utilization of new memory technologies; the hardware design for supporting data base operations in a data base machine; the interconnection structure between memories and processors; etc. must be considered in the design.

#### 1.2.3 Issues in Operational Control

These issues are concerned with the efficient, correct, reliable and secure operations of the data base. They can be classified into:

### (A) Resource Management of Data

These are issues related to the management of data and files as resources of the system so that multiple users can share the files on the data base efficiently [RAM79a]. The control of files as resources is not only applied at the file level, where the files have to be placed at nodes easily accessible to users and the data have to be compressed for efficient communication and storage, but it ranges from the users' level to the physical level. On the users' level, the queries have to be processed so that the amount of data movements is minimum. On the physical level, the individual file requests have to be sequenced so that maximum hardware parallelism can be achieved. Some of these issues are the focus of study in this thesis.

#### (B) Concurrent Accesses and Updates

In a DDB where users share the same data, there are several problems associated with multiple accesses and updates. When users try to access the common data, there would be interference among the accesses, and the communication protocol should be designed to minimize this interference. Another problem related to consistency arises when data elements with multiple copies at different locations are to be updated. Simple locking mechanisms cause excessive delays and may cause throughput degradation in the DCS. Efficient updating schemes are needed and the architectures would be very much influenced by such schemes [ESW76].

## (C) Directory Management

The directory is a special file in which the addresses for various files on the system are provided. Each access to a file must therefore pass through the directory. Due to the high intensity of the accesses on the directory, special attention must be paid to its design. In particular, the designer has to consider the type of directory structure which is most suitable for his application and whether the directory should be replicated or partitioned. In general, a combination of replication and partition is used. Further, reliability considerations must be made in the design of the directory [ROT77].

## (D) Security and Privacy

Another important issue in the design of a DDB is security and privacy. Security refers to the protection of data against deliberate or accidental destruction, unauthorized access or modification of data. On the other hand, privacy refers to the right of an individual user to determine for himself what personal information to share with others as well as what information to receive from others. As the size of the data base increases, the threat to security and privacy increases. In addition, it is increasingly difficult to implement effective measures in a DDB. Additional techniques such as data encryption would affect the transmission efficiency and the communication mechanisms [BAD78, DOW77].

#### (E) Reliability - Rollback and Recovery

The determination of the necessary hardware for reliable operations, the data redundancy and the reconfiguration strategies are another major issue in the design of a DDB. Multiple copies of data base realm offer fast recovery; checkpointing of realms, dumping and journal rollback and roll-forward offer a slower but cheaper recovery. The effect of any recovery mechanism and reconfiguration strategy on the response time and the associated overhead must be weighed against the reliability requirements [KRI78].

#### 1.2.4 Issues in Evolution

In order for the system to be able to adapt to new application requirements and technology advancements, evolutionary measures must be incorporated into the system at the design stage. Three of the contradicting issues of evolution are:

#### (A) Technology Dependence

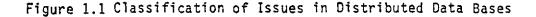

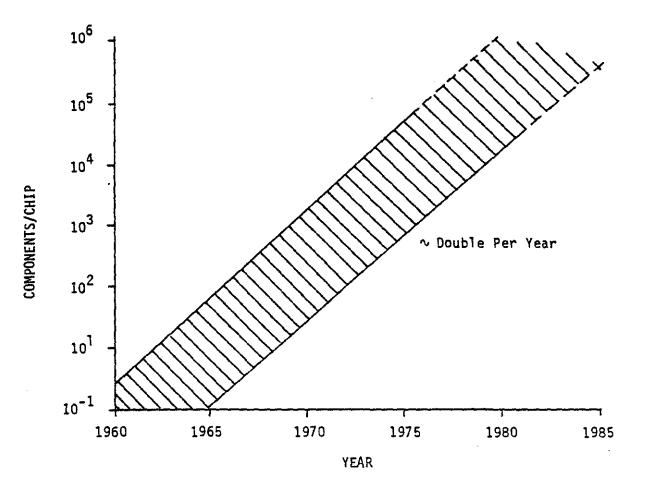

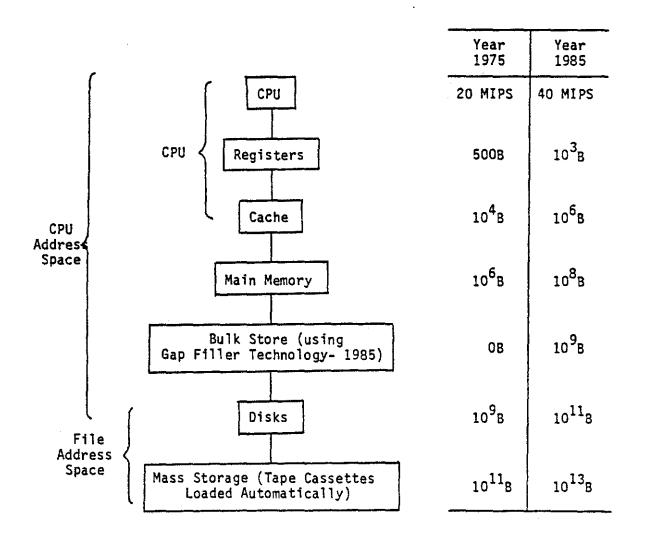

Technology is one of the most important driving force for the success of a computer system. As seen in Figures 1.2 and 1.3, the number of components per chip is approximately doubling each year, and the CPU speed is growing exponentially each year. These faster and denser logic, together with a variety

Figure 1.2 The Density Growth of Large Scale Integrated Circuits

Figure 1.3 The Exponential Growth of CPU Speed

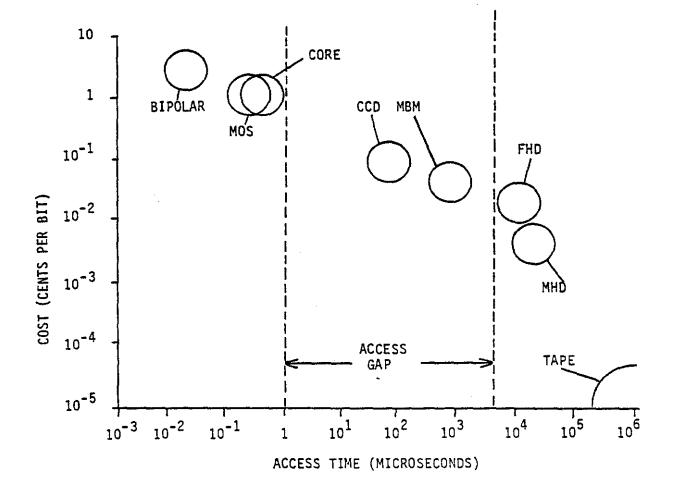

of device manufacturing technologies [MOE78], offer a variety of semiconductor memories with different access times and prices [THE78, UPT78, FET76]. In Table 1.2, the typical access time and power consumption for several semiconductor memory types are shown. Given these diverse types of memories available on the market, the designer must therefore decide at the design stage the most suitable memory to use. Moreover, magnetic device technologies have also improved significantly. With the improvement of disks, drums and tapes, the invention of the bubble memories [BOB71], and the Electron Beam Access Memories (EBAMs) [HUG75], it is now possible to provide inexpensive secondary and archival storage to the computer system (see Figure 1.4).

With these evolving technologies, there are three significant impacts on the design of computers. First, new technologies add extra design alternatives to the designers which allow the designers to design a system with improved performance and decreased system complexity. An example is shown by the recent developments of bubble memories, CCD memories and EBAMs which have emerged to fill the "access gap" between the two traditional memory technolo-

| Memory<br>Type              | Access<br>Time (nsec) | Power Con-<br>sumption (mw) | Approx. Price<br>(¢/bit) |

|-----------------------------|-----------------------|-----------------------------|--------------------------|

| 16K MOS dynamic             | 125-300               | 400-600                     | 0.30                     |

| 4K NMOS dynamic             | 150-350               | 460                         | 0.33                     |

| 4K ECL static               | 30                    | 1000 -                      | 0.85                     |

| 4K I <sup>2</sup> L dynamic | 120                   | 450                         | 0.59                     |

| 4K TTL static               | 50-70                 | 600-900                     | 0.80-1.00                |

| 4K MOS static               | 55-170                | 30-500                      | 0.61-0.92                |

| 1K CMOS static              | 150                   | 4                           | 1.02                     |

| 1K TTL static               | 40-100                | 500-800                     | 0.95                     |

| 1K ECL static               | 35-60                 | <u>500-800</u>              | 1.30                     |

Table 1.2 Typical values for LSI Semiconductor RAMs (1978) (Price is shown for quantities of 100)

Figure 1.4 Availability of New Memory Technologies

gies (see Figure 1.4). The access gap is the region characterized by an access time between  $10^{-6}$  sec. (MOS memories) and  $10^{-3}$  sec. (fixed head magnetic disk). Much time and effort is expended in finding efficient ways to accomplish at minimum cost the necessary transfers of information across the access gap. With the utilization of "gap-filler" technologies, improved performance and less complex transfer algorithms can be envisioned. Second, increasing logic on a chip allows the designer to incorporate more logical capabilities into the storage sub-system in addition to the storage capabilities. These logical capabilities include abilities to execute arithmetic operations like summation, averaging, as well as logical operations like maximum/minimum searches, equality search, etc. The designer has to decide on the necessary logical capabilities in the system and how they should be designed. The last impact of changing technologies on computer system design is the increasing speed mismatch among the elements of the computer system. With the development of high speed processors such as the CRAY-1 and multi-processor system such as the C.mmp, there is an increasing need of higher bandwidth from the supporting memory sub-system. In order to improve the bandwidths of memories, it is necessary to have intelligent architectural designs and efficient access algorithms for supporting retrieval operations in addition to the utilization of faster memory components. Special emphases should therefore be placed on the utilization of new technologies, the design of new memory architectures and the study of efficient access algorithms.

Evolving technology allows the users more freedom in specifying and operating the system. More stringent requirements can be specified and many of the system's functions can be designed in hardware. However, the dependence of the system on evolving technologies is usually a severe constraint on the designer, and the evolutionary capabilities of a system depend very heavily on how well the designer can predict the future technologies.

## (B) Application Dependence

Because the size and the complexity of applications change with time, the design of the system may have to be altered after the system has been deployed. However, much too often, systems are designed without taking into account the provision for future changes. When the system evolves, the changes are incorporated into the system in a very disorganized manner. As a result, the unstructureness of the system increases enormously [BEL77] and leads to a regenerative, highly non-linear increase in the effort and cost of the system maintenance [LEH76]. In addition to this, the reliability and the integrity of the system are also jeopardized greatly. One provision is to have a systematic design and development methodology which provides guidelines for the systematic design and construction of DDBs and allows the system to evolve as the application requirements and technology change [RAM78b, RAM79b].

## (C) Standardization

One of the major inhibiting factors in the development and evolution of DDBs is the lack of standardization in the areas of programming languages, user interface commands, data models, concurrency control mechanisms, hardware components (e.g. disks, tapes), data formats, network protocols, etc. Standardization of hardware and software components allow modular expansion of the system. On the other hand, with a highly evolving technology, standardization may cause costly refitting later and may even hinder acceptance of new ideas.

We have outlined some of the issues in the design of a distributed system supporting a DDB. These issues are by no means complete and other issues, both design and operational, have to be considered. Alternative solutions to these issues provide the options to be decided upon by the designers during the design phase of the system.

## 1.3 ARCHITECTURE OF THE SYSTEM SUPPORTING A DDB

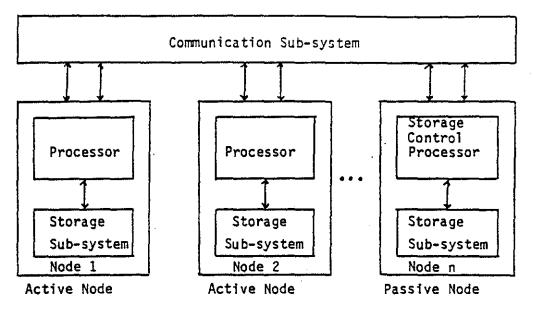

The memory system on a DCS is made up of nodal memories connected together by a network and communicates via the connected processors (Fig. 1.5a). Each node in the system, which consists of a set of processing elements and the supporting storage sub-system, may be active or passive. If the node is active, it acts as a requesting source and can access the memories at other nodes via the communication sub-system. Each of the active nodes in the system has the following functions in addition to the local file accesses.

(1) Remote access control

This module detects all remote access requests originating from this node and is responsible for processing them. When a remote request is detected, this module looks up the network directory, and assesses the file status. If the file exists on the network and is accessible by the request, this request will then by transmitted.

## (2) Local access control

This module is responsible for processing all remote requests received from other nodes in the network. It acts as a security filter and determines whether the file is accessible. If so, the local file is accessed and the data will be transmitted.

## (3) Redundant file maintenance control

This module coordinates all the local and the remote updates at this node and manages the multiple copies of files on the system. In coordinating updates, if the update originates from a remote node, the status of the file is checked. In case that a conflict occurs and the data cannot be updated, a status message is sent. On the other hand, if no conflict occurs, the file is updated. If the update originates at this node, this module looks up the network directory and sends out all the requested

(a) A DCS Memory System

(b) Functional Design of an Active Node

Figure 1.5 Architecture of a DDB System

updates to every redundant copy on the system.

The relation of these modules to each other in an active node is shown in Fig. 1.5b. The logical issues in a DDB, such as security and privacy, concurrency control, etc., are resolved in these modules.

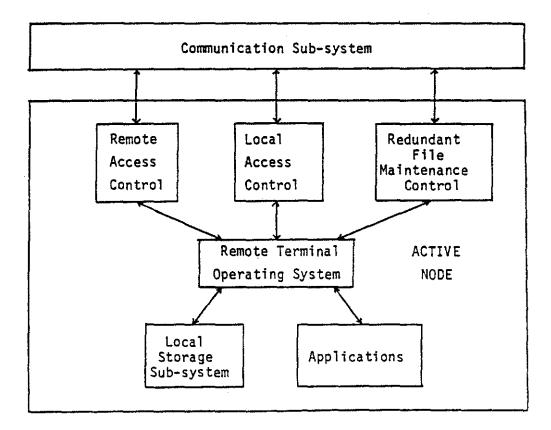

On the other hand, the physical storage system at a node comprises a memory hierarchy that stores programs and data. It has been realized for a long time that the conflicting requirements for high performance and low cost storage sub-system at a node can be satisfied by a combination of expensive high performance devices with inexpensive low performance devices which results in a memory hierarchy. The spectrum of storage devices ranges from bulk store and magnetic tape on one end, to the fast register storage and cache memory in the CPU on the other hand (Figure 1.6). Many issues have to be considered when these different speed elements are put together. These include: the selection of some physical parameters such as the number of levels in the hierarchy and the size and the speed of each level [RAM70, WAR76]; the design of the interconnection mechanism among levels [SMI76, POH75]; the design of efficient scheduling algorithms and record/file distribution and migration algorithms [MUN74, STR77]; the provision of virtual memory support for an automatic file management system [TUE76, POH75, DEN70, BAS70], etc. The last issue is particularly important because the success of a DB is very much dependent on the efficiency of the virtual memory. A file on a DB is likely to be large and cannot reside entirely in the main memory. The use of virtual memory can relieve the users from the laborious task of storage management. It is seen that research is urgently needed in this area.

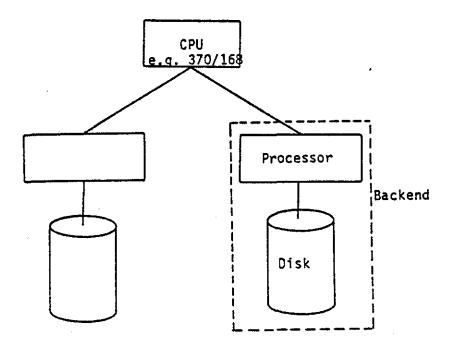

There is also an increasing tendency to distribute the processing of the CPU to the various levles of the storage sub-system. One successful implementation of this is the DB machine (Figure 1.7) [HSI77]. The DB machine may be a

÷.

Figure 1.6 Storage Hierarchy (With Typical Sizes shown for 1975 and 1985)

Figure 1.7 Architecture of a Data Base Machine

separate member of the storage sub-system or it may represent a level of the memory hierarchy with additional intelligence. The use of a DB machine relieves the processing load of the central processor and allows more parallelism in the processing of DB requests. Further, processing on large file systems are often I/O bound and many of the file operations are quite simple. A significant communication overhead is incurred in transferring the file to a level of the memory hierarchy where the processor can access it. By distributing the intelligence to the different levels of the memory hierarchy, the DB machine can allow parallel processing with very little communication overhead.

Although DB machines have been successfully designed or implemented, e.g. Data Base Computer (DBC) [BAU76], Context Addressed Segment Sequential Storage (CASSM) [LIP78], Relational Associative Processor (RAP) [OZK77], Rotating Associative Memory for Relational Data Base Applications (RARES) [LIN76], Datacomputer [MAR75], etc., the design of DB machines are still plagued by many issues. Examples of these issues are: deciding on the kind and the degree of parallelism; selecting the appropriate techniques for implementing the storage media; designing the hardware and the software interface; building the storage structure and the backend primitives and designing the control algorithms. These issues are very important because the storage sub-system is very expensive and can be more than 50% of the total hardware system cost [SCH78]. Some of these issues are discussed in Chapter 5 of this thesis.

This section has described some of the necessary architectures in supporting DDB applications. Data base processing generally has some special characteristics and these allow the architecture to be designed differently from conventional architectures. In the next section, the issues on the resource management of data on a DDB are discussed.

#### 1.4 OBJECTIVES AND CONTRIBUTIONS OF THIS RESEARCH

#### 1.4.1 Problem Statement

The primary objectives of this research effort are the development of a realistic, comprehensive, analytical model for the management of data as resources on a DDB. This design problem encompasses the issues of establishing a systematic way of classification of the different levels of resource management in a DDB, design of performance measures for each level and development of procedures for the optimal solution for certain problems in each level. We hope to provide a strong framework for future research into problems associated with these large scale systems as well as the solutions to some specific design problems.

# 1.4.2 Approach

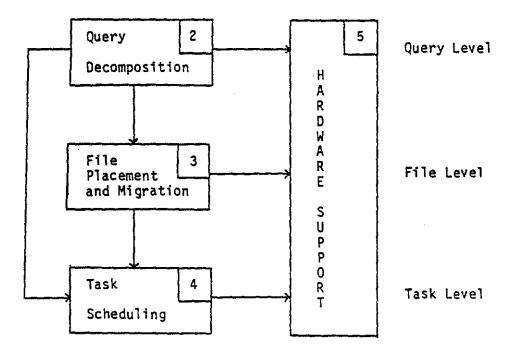

In order to achieve the global objective, the resource management issues are classified into four related levels, namely, the query level, the file level, the task level and the hardware support level. The specific data management issues investigated are:

#### (1) Query Decomposition on DDB's

A query is an access request made by a user or a program in which one or more files have to be accessed. When multiple files are accessed by the same query on a DDB, these files usually have to reside at a common location before the query can be processed. Substantial communication overhead may be involved if these files are geographically distributed and a copy of each file has to be transferred to a common location. It is therefore necessary to decompose the query into sub-queries so that each sub-query accesses a single file. These sub-queries may then be processed in parallel at any location which has a copy of the required file. The results after the processing are sent back to the requesting location. It is generally true that the amount of communications needed to transmit the results is much smaller than the amount needed to transmit the files. This approach has been proposed in the design of the centralized version of INGRES [WON76] and is extended to the design of SDD-1 [WON77], and distributed INGRES [EPS78]. However, in some cases, decomposition is impossible and some file transfers are still necessary. Two techniques are proposed in Chapter 2 so that the overall operational costs of the system can be reduced.

### (2) File Placement and Migration

This issue relates to the distribution and migration of data base components, namely, files and control programs, on the DDB with the objective of minimizing the overall storage, migration, updating and access costs on the system. A file assignment algorithm is proposed in Chapter 3.

### (3) Task Scheduling

Requests on the DDB must be scheduled so that high parallelism and overlap can be achieved. The request may be a single word fetch or it may be a page or file access. This parallelism is important because in order to attain high throughput, the parallel hardware and resources must be efficiently utilized. The control of task scheduling can be distributed or centralized. In distributed control, each node may act independently and coordinate with each other. In centralized control, there is a primary node in which all scheduling control are performed. The decision of which is the better control mechanism depends very heavily on the interconnection structure and the communication overhead involved. This issue is discussed in Chapter 4.

### (4) Hardware Support

In addition to studying the logical data management techniques, the

design of the necessary hardware support is also very important. This hardware does not necessary implement a solution to one of the data management issues, e.g. file placement, but it provides auxillary support to these solutions so that they can be implemented efficiently. The particular hardware supports studied are the associative memory and the data base machine. These are discussed in Chapter 5.

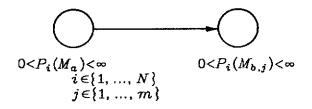

The relationships among the various data management issues are shown in Figure 1.8 where a relation  $\rightarrow$  is said to exist between two design issues  $\alpha$ ,  $\beta$ , i.e.  $\alpha \rightarrow \delta$  if the solution of  $\delta$  is transparent to the solution of  $\alpha$ . That is, the solution of  $\boldsymbol{\sigma}$  is not affected by the solution to  $\boldsymbol{\delta}$ , but not vice versa. The solution to  $\boldsymbol{\sigma}$ can therefore be developed independent of  $\mathcal{F}$ . In Figure 1.5, it is seen that generally, task scheduling is transparent to file placement and migration which in turn could be transparent to query decomposition. Further, hardware support is transparent to all these logical issues and are generally developed after the algorithms for the logical issues have been designed. Due to the independency, algorithms for query decomposition can be developed independently. In developing algorithms for file placement and migration, the solutions for query decomposition should be taken into account. However, in most cases, assumptions can be made about their solutions and the file placement and migration problem can be solved independently. For example, it may be assumed that all queries which access multiple files may be decomposed into sub-queries that access single files. This assumption is only true in some circumstances, an example of which is shown in Chapter 2 of this thesis. The file placement and migration problem for multiple files is therefore decomposed into many single file optimization sub-problems. It must be noted that other operational control requirements may also impose restrictions on the solutions to the data management issues. For instance, different reliability requirements may demand different lower bounds on the number of copies of a file on the DDB; different

Figure 1.8 Relationships Among Various Data Management Issues (The Number in Each Issue Indicates the Chapter in which it is Discussed)

concurrency control mechanisms may have different costs on the file placement problem; etc. Reasonable assumptions must therefore be made about these techniques in order to determine their effects on the resource management issues and to solve these issues independently.

#### 1.4.3 Contributions of this Research

Some specific contributions of this research, arranged in the order of discussion, are listed below.

- (A) A model for query decomposition on relational data bases has been developed. It is shown that the optimization of placements of multiple relations can be done independently for each relation.

- (B) Two cost reduction models have been designed to reduce the operational costs of a relational data base. The first model reduces the retrieval cost, but increases the update cost. The second model reduces the update cost but increases the retrieval cost. These two cost reduction models can be combined to form a unified approach to reduce the operational costs of the DDB's. Further, it is also shown that the optimization of placements of multiple relations under the use of these techniques can be done independently for each relation.

- (C) The isomorphism between the file placement problem and the single commodity warehouse location problem has been proved. Due to this isomorphism, it is also shown that some conditions and techniques developed in computer science to solve the file placement problem are weaker than the corresponding conditions and techniques developed in operations research to solve the warehouse location problem, and vice versa. Further, the technique developed in both problems are inter-changeable.

- (D) A file placement heuristic has been developed. While not necessarily yielding optimal system design, this heuristic yields solutions of lower cost than

those generated by other currently available heuristics.

- (E) A model for the scheduling of tasks on a distributed system has been developed. This model assumes that global control is infeasible and all the scheduling decisions have to be made locally at each node. It is shown that the scheduling of tasks in this model when all the task processing times are deterministic, is an NP-complete problem. A heuristic has been developed and the performance of this heuristic has been verified using simulations.

- (F) A more restricted model than the model developed for the scheduling of tasks on a DCS has been proposed. By using the additional constraints, it is shown that the optimal scheduling problem is polynomially solvable. This model actually represents an organization of an interleaved memory system. The performance of the scheduling algorithm has been verified using simulations. Further, the degradation in performance due to dependencies has been estimated.

- (G) An associative memory has been designed which is capable of searching the maximum and the minimum in a time independent of the number of words in the memory. It is also capable of doing equality search, threshold searches and proximity search. The design is very efficient and has a complexity of 17 gates per cell. The design is asynchronous and utilizes a word-parallel and bit-serial algorithm. The delay is 1 to 4 gate delays across each bit slice.

- (H) The associative memory concept is extended to the design of data base machines. The logic designed can be implemented on the same chip as the memory elements.

### 2. QUERY DECOMPOSITION ON A DISTRIBUTED RELATIONAL DATA BASE

In this chapter, the problems of query decomposition and its association with the optimal placements of relations on a distributed relational DB are studied. Our objectives are to study techniques which allow query decomposition to be done more efficiently and to investigate properties on the optimal placements of multiple copies of relations or segments of relations on the DCS that minimize the total operational cost of the system (e.g. storage cost, multiple update cost, retrieval cost, query processing cost, file migration cost, etc.). The theme of this chapter is to demonstrate that the placements of multiple relations on a distributed relational DB can be optimized for each relation independently. It is assumed that a technique exists to find the optimal placements of multiple copies of a single relation on a DDB, an example for which is shown in Chapter 3. In this chapter, two methods have been proposed to reduce the operational costs of the system. The first method utilizes additional redundant information on the DDB so as to reduce the total retrieval cost and increase the total update cost. The second method uses file partitioning to reduce the total update cost and increase the total retrieval cost. It is shown by an example DB, that under certain conditions, either method, or a combination of both methods, can reduce the total operational costs of the system. A relational data model is chosen in this discussion because it is very popular and the results obtained would be more specific. However, the techniques proposed in this chapter can be generalized to any type of data model and file system.

### 2.1 QUERIES ON A RELATIONAL DB

In a relational DB [COD70], data is viewed as relations of varying degree, the degree being the number of distinct domains participating in the relation. Each instance of a relation is known as a tuple, which has a value for each domain of the relation. Thus a relation can simply be represented in tabular form with columns as domains and rows as tuples.

A Query is an access request made by a user or a program, in which one or more relations have to be accessed. A query on a relational DB consists of two parts: the part specifying the domain(s) of the relation to be retrieved and the part specifying the predicate which is a quantification representing the defining properties of the set to be accessed. Let S be a relation of domains s#, sname, city, inventory; and SP be a relation of domains s#, p# (Figure 2.1). The queries on a relational DB can be classified into the following categories [DAT77]:

- (1) Retrieval Operations

- (a) Single Relation Retrieval: The predicate representing the defining property of the set to be retrieved is defined on the same relation as the set.

(a) Relation S

| S | s# sname |            | city          | inventory |  |

|---|----------|------------|---------------|-----------|--|

|   | 1        | Supplier A | New York      | 1500      |  |

|   | 3        | Supplier B | San Francisco | 700       |  |

|   | 5        | Supplier C | Chicago       | 2500      |  |

(b) Relation SP

| SP | s#     | P# |

|----|--------|----|

|    | 1      | A1 |

|    | 2<br>3 | A1 |

|    | 3      | A2 |

|    | 4      | A2 |

|    | _5     | P2 |

Figure 2.1 Relations S and SP

E.g. GET (S.sname): (S.city="Paris" AND S.inventory>1000)

- (b) Multiple Relation Retrieval: The predicate, as well as the set to be retrieved, may be defined over multiple relations.

E.g. GET (S.sname): (S.s#=SP.s# AND SP.p#="P2")

Relations S and SP must be available simultaneously before the retrieval can be processed.

- (2) Storage Operations

- (a) Single Relation Update;

- (b) Multiple Relation Update:

- (c) Insertion;

- (d) Deletion.

- (3) Library Functions

These represent more complicated operations on the predicate than the equality operations, e.g. counting the number of occurences, selecting the maximum/minimum etc.

Single relation queries can be processed very easily on a distributed relational DB. When the relation is geographically distributed, the query can be sent to a node that has a copy of the relation and be processed there. The results after the processing can be sent back to the requesting node. It is generally true that the amount of communications needed to transmit the results is much smaller than the amount needed to transmit the relations.

On the other hand, the processing of a mult-relation query is more complicated. When multiple relations are accessed by the same query on a DDB, these relations usually have to reside at a common location before the query can be processed. Substantial communication overhead may be involved if these relations are geographically distributed and a copy of each relation has to be transferred to a common location. It is therefore necessary to decompose the

query into sub-queries so that each sub-query accesses a single relation. This technique has been proposed in the design of the centralized version of INGRES [WON76], and is extended to the design of SDD-1 [WON77] and distributed INGRES [EPS78]. Specifically, the technique consists of two steps. The first step is to select a site with the minimum amount of data movements to that site before the query can be processed. This is used as a starting point for the second step of the algorithm which determines the sequence of moves that results in a minimum cost. The algorithm used is a greedy algorithm and only local optima can result from such an algorithm. Hevner and Yao [HEV79] have followed a similar approach and have developed two optimal algorithms for arranging data transmissions and local data processing with minimal response time and minimal total time, for a special class of queries. These optimal algorithms are used as a basis to develop a general query processing algorithm for a general query in which each required relation may have any number of joining domains and output domains and each node may have any number of required relations. This general algorithm is a heuristic which uses an improved exhaustive search to find efficient query distribution strategies. Ghosh also proposed a model of data distribution on a DB which facilitates query processing [GH076]. Specifically, the model consists of a DB with multiple target segment types and there are queries with multiple target segment types. The objective is to distribute the segments on the DB so as to maximize the number of segments that the queries can retrieve in parallel from different nodes. The model only looks at the problem from a retrieval point of view and no cost is associated with retrieving a segment from a node.

Most of the previous work addresses the problem from two separate viewpoints. The first one is concerned about the questions of what are the processing sequence of the query and where it should be processed. The second viewpoint is concerned about where the files should be placed so that they can be accessed efficiently. These two viewpoints are not entirely independent and should be investigated together. Further, there exists queries which are nondecomposable. For example, the query:

GET (S.sname):  $(S.s\#=SP.s\#AND SP.p\#="P_2")$

is not decomposable into single relation retrievals because there is a logical relation "=" which is defined over a common domain s# of the relations S and SP. These relations must be available simultaneously at a common location before the retrieval or update operations can be performed. Instead of solving the problem of decomposing the queries, we study two techniques to reduce the processing and communication costs for non-decomposable queries in this chapter. It is shown later, by the introduction of some redundant information on the DB and by the use of file partitioning, non-decomposable queries may be made decomposable, (see also [RAM79a, RAM79c]). The basic assumption made over here is that all the required relations are moved to the node at which the query originates, before the processing of the query begins. It is possible to consider a sequence of moves which will minimize the total amount of data transferred. However the problem will be very complicated and the intention of this chapter is to demonstrate the usefulness of the techniques of using redundant information and file partitioning.

Before the techniques are discussed, the problem of placements of relations on a DDB is first formulated.

### 2.2 THE PLACEMENTS OF RELATIONS ON A DDB

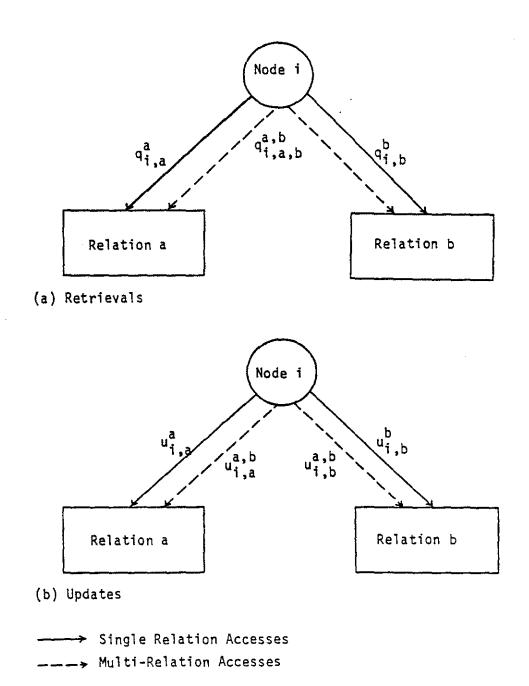

In this section, a model for the placements of multiple relations on a DDB is formulated. The model is shown for the special case of two relations and is generalized later to the case of more than two relations. Consider two relations a and b, the retrieval and the update rates at node i are (see Figure 2.2)<sup>1</sup>:

- $q_{i,a}^{a}(q_{i,b}^{b}) =$  rate of access at node i for a single relation retrieval accessing relation a(b);

- $q_{i,a,b}^{a,b}$  = rate of access at node i for a multi-relation retrieval accessing both relations a and b;

- $u_{i,a}^{a}(u_{i,b}^{b}) = rate$  of update at node i for a single relation query updating relation a(b);

- $u_{i,a}^{a,b}(u_{i,b}^{a,b}) =$  rate of update at node i for a multi-relation query accessing both relations a and b before updating relation a(b).

The costs for each unit of access are:

- $S_{i,j}^{a}(S_{i,j}^{b}) =$ communication and processing cost per unit query of accessing relation a(b) from node i to node j;

- $M_{i,j}^{a}(M_{i,j}^{b})$  = communication and processing cost per unit update of multiple updating relation a(b) from node i to node j.

We differentiate between the costs of retrievals and updates because in some applications, retrievals are more important than updates and therefore would have a higher cost (e.g. inventory system); while in other real time applications, updates may be more frequent and therefore more critical (e.g. airline reservation system). Let:

n = number of nodes on the DCS;

<sup>&</sup>lt;sup>1</sup> The conventions of the symbols used are as follows: i,j represent indexes for nodes; a,b represent indexes for relations; the superscripts represent the list of relations that the query must access before the query can be processed; the subscripts represent the nodes concerned and the tar-

$l_a(l_b) = \text{length of relation } a(b);$

$f_{i,a}(f_{i,b}) = \text{per unit cost of storing relation } a(b)$  at node i.

We define from the characteristics of the queries initiated from node i, the following symbols:

(1) Single relation retrievals:

$\alpha_{i,a}^{a}(\alpha_{i,b}^{b}) =$  fraction of relation a(b) that is put into the result relation due to the execution of a single relation retrieval on a(b);

(2) Multi-relation retrievals:

$\alpha_{i,a}^{a,b}(\alpha_{i,b}^{a,b}) =$ fraction of relation a(b) that is needed to process a multirelation retrieval on a and b;

(3) Single relation updates:

$\beta_{i,a}^{a}(\beta_{i,b}^{b}) =$  fraction of relation a(b) that will be updated by a single relation update;

(4) Multi-relation updates:

$\nu_{i,a}^{a,b}(\nu_{i,b}^{a,b}) =$ fraction of relation a(b) that is needed to process a multirelation update before the updates can be performed;

$\beta_{i,a}^{a,b}(\beta_{i,b}^{a,b}) =$  fraction of relation a(b) that will be updated by a multi-relation update after relations a and b have been accessed.

In processing a multi-relation update, the relations a and b must be accessed first in order to determine what are the actual updates that have to be made. This is measured by the parameters  $\nu_{i,a}^{a,b}$  and  $\nu_{i,b}^{a,b}$ . The fraction of relations a

get list of relations for the query.

and b to be updated after they have been determined are measured by the parameters  $\beta_{i,a}^{a,b}$  and  $\beta_{i,b}^{a,b}$ .

The parameters defined above can be estimated from the characteristics of the different types of queries that can be made on the DDB and the probability distribution of the data stored in the relations.

The control variables governing the file locations and the routing discipline are defined as follows:

$$Y_i^a(Y_i^b) = \begin{cases} 0 & \text{if relation } a(b) \text{ does not exist at node } i \\ 1 & \text{otherwise} \end{cases}$$

$$X_{i,j}^a(X_{i,j}^b) = \text{fraction of queries made at node } i \text{ on relation } a(b) \text{ that are routed to node } j.$$

It is true that if  $X_{i,j}^r > 0$ , then  $Y_j^r = 1$  for r=a,b.

The optimization problem of placing relations a and b on the DDB can be formulated in the following linear program:

$$\sum_{r=a,b} \sum_{i=1}^{n} \sum_{j=1}^{n} q_{i,r}^{r} \alpha_{i,r}^{r} l_{r} X_{i,j}^{r} S_{i,j}^{r}$$

(2.1a)

+

$$\sum_{r=a,b} \sum_{i=1}^{n} \sum_{j=1}^{n} q_{i,a,b}^{a,b} \alpha_{i,r}^{a,b} l_r X_{i,j}^r S_{i,j}^r$$

(2.1b)

$$+\sum_{r=a,b}\sum_{i=1}^{n}\sum_{j=1}^{n}u_{i,r}^{r}\beta_{i,r}^{r}l_{r}M_{i,j}^{r}Y_{j}^{r}$$

(2.1c)

$$+ \sum_{r=a,b} \sum_{i=1}^{n} \sum_{j=1}^{n} u_{i,r}^{a,b} \bigg[ \sum_{s=a,b} \nu_{i,s}^{a,b} l_{s} X_{i,j}^{s} S_{i,j}^{s} + \beta_{i,r}^{a,b} l_{r} M_{i,j}^{r} Y_{j}^{r} \bigg]$$

(2.1d)

+

$$\sum_{r=a,b} \sum_{i=1}^{n} f_{i,r} l_r Y_i^r$$

(2.1e)

subject to the following constraints:

$$\sum_{i=1}^{n} Y_i^r \ge 1 \qquad r=a,b \qquad (2.1f)$$

$$\sum_{j=1}^{n} X_{i,j}^{T} = 1, \qquad r = a, b, i = 1, 2, ..., n$$

(2.1g)

$$nY_j^r \ge \sum_{i=1}^n X_{i,j}^r \ge 0, \quad r=a,b, \ j=1,2,...n$$

(2.1h)

$$Y_i^r = 0, 1, \quad r = a, b, i = 1, 2, ..., n$$

(2.1i)

Eq. 2.1a represents the access cost for single relation retrievals; Eq. 2.1b represents the access cost for multi-relation retrievals; Eq. 2.1c represents the update cost for single relation updates; Eq. 2.1d represents the update cost for multi-relation updates and Eq. 2.1e represents the storage cost of relations on the DDB. Condition 2.1f assures that at least one copy of the relation exists; condition 2.1g assures that all the queries are serviced; condition 2.1h assures that the relation must exist at a node if a route is defined to access it at that node and condition 2.1i assures that the control variables  $Y_i^r$  are integral.

### LEMMA 2.1

The above optimization problem can be partitioned into two independent optimization sub-problems, one for each relation:

(a) min

$$\sum_{i=1}^{n} \sum_{j=1}^{n} Q_{i}^{a} X_{i,j}^{a} S_{i,j}^{a} + \sum_{i=1}^{n} \sum_{j=1}^{n} U_{i}^{a} M_{i,j}^{a} Y_{j}^{a} + \sum_{i=1}^{n} F_{i}^{a} Y_{i}^{a}$$

where

where

$\begin{aligned} Q_i^a &= (q_{i,a}^a \alpha_{i,a}^a + q_{i,a,b}^{a,b} \alpha_{i,a}^{a,b} + u_{i,a}^{a,b} \nu_{i,a}^{a,b} + u_{i,b}^{a,b} \nu_{i,a}^{a,b}) l_a \\ U_i^a &= (u_{i,a}^a \beta_{i,a}^a + u_{i,a}^{a,b} \beta_{i,a}^{a,b}) l_a \\ F_i^a &= f_{i,a} l_a \\ subject to: \end{aligned}$

$$\sum_{i=1}^{n} Y_i^a \ge 1$$

$$\sum_{j=1}^{n} X_{i,j}^a = 1 \qquad i = 1, \dots, n$$

$$nY_j^a \ge \sum_{i=1}^n X_{i,j}^a \ge 0 \qquad j = 1,...,n$$

$$Y_i^a = 0, 1 \qquad \qquad i = 1,...,n$$

(b) min

$$\sum_{i=1}^{n} \sum_{j=1}^{n} Q_{i}^{b} X_{i,j}^{b} S_{i,j}^{b} + \sum_{i=1}^{n} \sum_{j=1}^{n} U_{i}^{b} M_{i,j}^{b} Y_{j}^{b} + \sum_{i=1}^{n} F_{i}^{b} Y_{i}^{b}$$

where

$$Q_{i}^{b} = (q_{i,b}^{b} \alpha_{i,b}^{b} + q_{i,a,b}^{a,b} \alpha_{i,b}^{a}^{b} + u_{i,a}^{a,b} \nu_{i,b}^{a}^{b} + u_{i,b}^{a}^{b} \nu_{i,b}^{a}^{b}) l_{b}$$

$$U_{i}^{b} = (u_{i,b}^{b} \beta_{i,b}^{b} + u_{i,b}^{a} \beta_{i,b}^{a}^{b}) l_{b}$$

$$F_{i,b} = f_{i,b} l_{b}$$

subject to:

$$\sum_{i=1}^{n} Y_{i}^{b} \ge 1$$

$$\sum_{i=1}^{n} X_{i,j}^{b} = 1 \qquad i = 1,...,n$$

$$nY_{j}^{b} \ge \sum_{i=1}^{n} X_{i,j}^{b} \ge 0 \qquad j = 1,...,n$$

$$Y_{i}^{b} = 0, 1 \qquad i = 1,...,n$$

### Proof

We notice in optimization problem (2.1) that there are no cross product terms in the control variables of relations a and b. Therefore, the objective function of (2.1) can be written as a sum of objective functions of optimization problems (2.2) and (2.3), and similarly, the constraints can be partitioned into two independent sets. The solution to (2.2) will therefore be a constant in (2.1)which implies that (2.3) can be solved independently. Similarly, the solution to (2.3) will be a constant in (2.1) and this implies that (2.2) can be solved independently.

Q.E.D.

(2.3)

We conclude that the optimization problem 2.1 for relations a and b can be carried out as two optimization sub-problems for relations a and b independently.

A further simplification of the integer programs (2.2) and (2.3) is to first solve for  $X_{i,j}^r$ , r=a,b, and substitute it into the integer programs. It is shown in [ALC76] that,

$$X_{i,j}^{T} = \begin{cases} \text{if } S_{i,j}^{T} = \min_{k, Y_{k}^{T}=1} S_{i,k} \\ 1 & \text{otherwise} \end{cases}$$

The detailed proof will not be shown here.

A generalization of Lemma 2.1 is to allow any number of relations in the DDB. This is shown in the following theorem.

#### THEOREM 2.1

The general problem of optimizing the placements of multiple relations on a DDB can be decomposed into multiple sub-problems, one for the placement of each relation.

The proof, which requires some symbols to be defined and can be done by obvious generalization of the proof of Lemma 2.1, will not be shown here.

The importance of Theorem 2.1 is that the original optimization problem of placing multiple copies of m relations on the DDB, which has a complexity of the order of  $O(2^{nm})$ , is reduced to m simpler optimization sub-problems of placing multiple copies of each relation on the DDB, each of which has a complexity of the order of  $O(2^n)$ . There are many techniques developed to place multiple copies of a relation on a DDB, e.g. [CAS72, LEV74, MOR77]. Some of these techniques are exhaustive and give optimal solutions, e.g. [CAS72, LEV74, MOR77]; others give sub-optimal solutions and have a polynomial running time, an example of which is shown in Chapter 3 of this thesis. In the remainder of this

chapter, we discuss two techniques to minimize the operational costs on the DDB. The costs with and without the application of these techniques are compared.

# 2.3 COST REDUCTION ON THE PLACEMENTS OF RELATIONS ON A DDB BY UTIL-IZING REDUNDANT INFORMATION